5.2.2. 功能描述

5.2.2.1. eFuse和SRAM空间映射

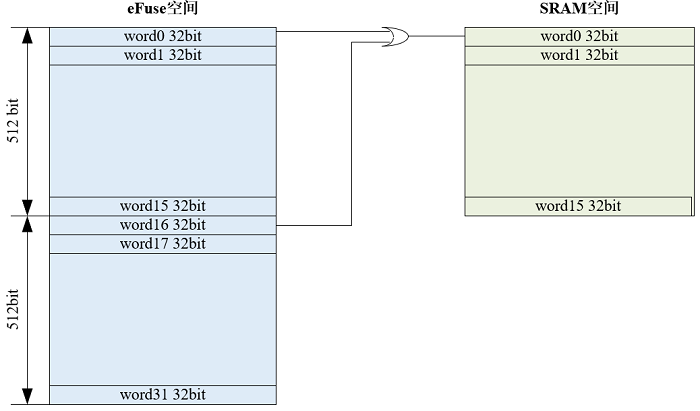

软件读写eFuse空间,在1K bit范围内以32bit为单位操作, 为达到可靠性,建议采用双备份方式,即写eFuse word[n]也写word[16+n]; 开机硬件自动读取eFuse空间到SRAM空间,针对两个word空间进行按位或操作, 任意一位为1则SRAM结果为1,起到双备份的目的, 如 图 5.5 所示。

图 5.5 eFuse和SRAM空间映射

5.2.2.2. 512bit空间映射定义

用途 |

位数 |

地址 |

禁止位 |

禁写 |

禁读 |

归属 |

备注 |

|---|---|---|---|---|---|---|---|

DIS |

32 |

0~3 |

0 |

CSTM |

15:00 eFuse 读禁止配置

31:16 eFuse 写禁止配置

每位对应1个32bits空间

|

||

BROM_SECURE |

32 |

4~7 |

1 |

V |

CSTM |

BROM 参数配置区域 |

|

CALI |

64 |

8~F |

2~3 |

V |

AIC |

模拟校准使用 |

|

CHIP ID |

128 |

10~1F |

4~7 |

V |

AIC |

芯片编号(子编号用到Reserved区域) |

|

SPI_ENC KEY |

128 |

20~2F |

8~11 |

V |

V |

CSTM |

安全,连接到 SPI_ENC,对称密钥 |

SPI_ENC NONCE |

64 |

CSTM |

此版本不可烧录,固定为某个值 |

||||

Reserved |

128 |

30~3F |

12~15 |

CSTM |

OEM 可自定义使用 |

5.2.2.3. BROM_SECURE 区域定义

比特位 |

名称 |

描述 |

|---|---|---|

31:29 |

- |

- |

28 |

SPI_ENC_EN |

BROM读取使用,使能SPI总线数据加密功能 |

27:25 |

- |

- |

24 |

JTAG_LOCK |

逻辑组合后连接到CPU屏蔽TDO,关闭JTAG调试功能,在安全方案中烧录为1 |

23:21 |

- |

- |

20 |

SDMC_EXT_MUX_DIV |

设置 SDMC 外部时钟选择 |

19:18 |

SDMC_SMP_PHASE |

设置 SDMC 采样时钟的相位 |

17:16 |

SDMC_DRV_PHASE |

设置 SDMC 驱动时钟的相位 |

15 |

CPU_HS_EN |

1:BROM 使能 CPU 高速模式,CPU 216 MHz,AXI/AHB 200 MHz |

14 |

CHECKSUM_DIS |

1:启动过程中 BROM 不检查固件的 Checksum |

13 |

PLL_FRA0_DIS |

1:BROM 不启用 PLL_FRA0 |

12 |

PLL_INT1_DIS |

1:BROM 不启动 PLL_INT1,USB 不能使用 |

11 |

SPI_DMA_DIS |

1:BROM 访问 SPI 存储时,不使用 DMA |

10 |

HWCHECKSUM DIS |

1: 启动过程中 BROM 不使用 DCE 检查固件的 Checksum,改为软件计算 Checksum |

9 |

SD/eMMC_DMA_DIS |

1:BROM 访问 SD/eMMC 时,不使用 DMA |

8 |

SKIP_SD_PHASE |

1:BROM 在访问 PRIMARY、SECONDARY 存储前不访问 SD 卡。设置为1影响卡量产 |

7:4 |

SECONDARY |

指定 BROM 的次选启动设备 |

3:0 |

PRIMARY |

指定 BROM 的首选启动设备 |

5.2.2.4. CALI区域定义

比特位 |

名称 |

描述 |

配置到寄存器 |

|---|---|---|---|

63:56 |

THS_ENV_TEMP |

THS 环境温度 |

|

55:44 |

THS_ADC_VAL |

THS1 采样值 |

|

43:32 |

THS_ADC_VAL |

THS0 采样值 |

|

31:24 |

OSC24_OUT_TR |

24MHz振荡器校准值 |

CMU 0x00A4 PLL_IN OSC_OUT_TR |

23:16 |

- |

- |

|

15:8 |

AVCC_BG_CTRL |

AVCC BG校准值 |

SYSCFG 0x020 LDO25_CFG BG_CTRL |

7:4 |

- |

- |

|

3 |

THS_VAL_VALID |

THS烧写值有效 |

|

2 |

OSC24_OUT_VDLID |

24MHz振荡器校准值有效 |

|

0 |

AVCC_BG_VALID |

AVCC BG校准值有效 |

5.2.2.5. CHIP ID(sub)区域定义(放在1C~1F bit19:0)

比特位 |

名称 |

描述 |

说明 |

|---|---|---|---|

19:8 |

- |

- |

- |

7:4 |

PSRAM_ID |

PSRAM编号 |

UBOOT读取后解析PSRAM参数 |

3 |

- |

- |

- |

1 |

CAN1_DIS |

CAN1锁定 |

CMU对CAN1总线时钟做逻辑锁定 |

0 |

CAN0_DIS |

CAN0锁定 |

CMU对CAN0总线时钟做逻辑锁定 |

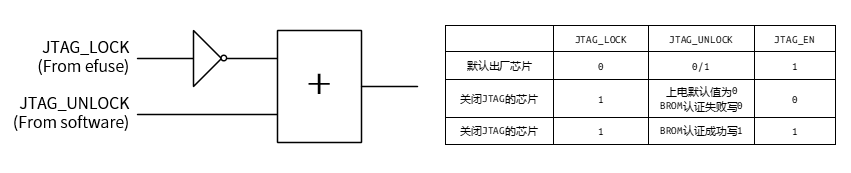

5.2.2.6. JTAG安全保护

JTAG使能受SID控制,用于对芯片做安全保护; 硬件逻辑及使用场景如 图 5.6 所示。

在关闭JTAG的安全芯片方案中,客户可以使用安全密钥进行认证, BROM在认证成功后开启UNLOCK位来打开JTAG, 注意JTAG_UNLOCK位只在BROM中进行读写(通过BROM_PRIVILEGE_LOCK实现)。

图 5.6 JTAG安全保护硬件逻辑及使用场景