9.4.2. 功能描述

9.4.2.1. LCD输出模式时序

LCD支持四种接口模式输出,分别为PRGB/SRGB/I8080/SPI。

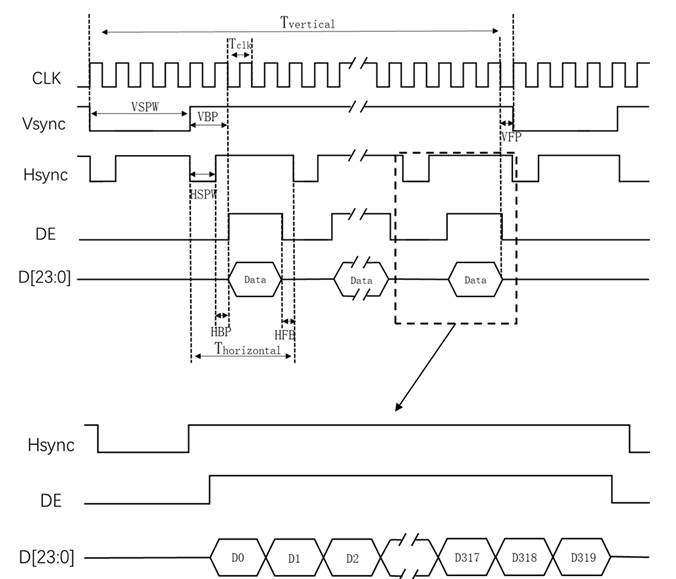

9.4.2.1.1. PRGB接口时序

图 9.19 PRGB接口时序

Defined |

Function |

|---|---|

Tclk |

时钟周期 |

Tvertical |

列扫描周期 |

Thorizontal |

行扫描周期 |

VBP |

列扫描后肩 |

VFP |

列扫描前肩 |

VSPW |

列同步信号脉宽 |

HBP |

行扫描后肩 |

HFP |

行扫描前肩 |

HSPW |

行同步信号脉宽 |

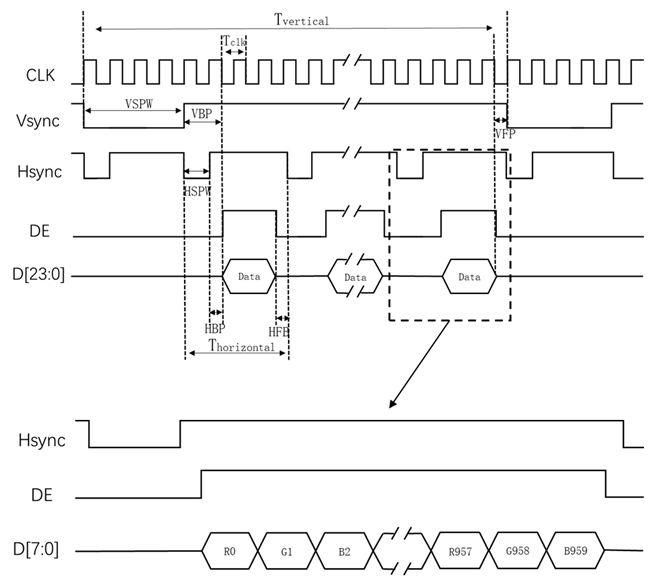

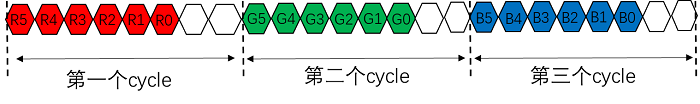

9.4.2.1.2. SRGB接口时序

图 9.20 SRGB接口时序

Defined |

Function |

|---|---|

Tclk |

时钟周期 |

Tvertical |

列扫描周期 |

Thorizontal |

行扫描周期 |

VBP |

列扫描后肩 |

VFP |

列扫描前肩 |

VSPW |

列同步信号脉宽 |

HBP |

行扫描后肩 |

HFP |

行扫描前肩 |

HSPW |

行同步信号脉宽 |

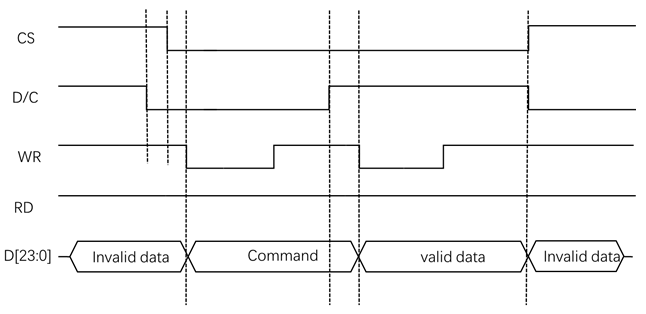

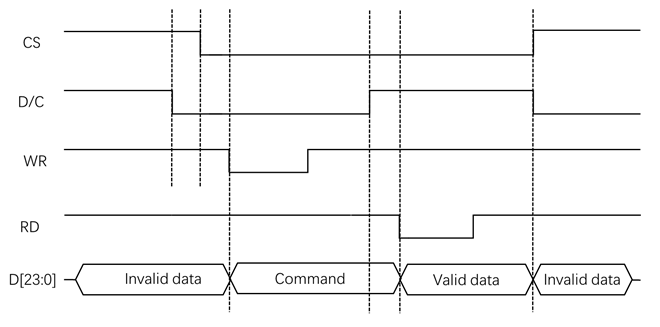

9.4.2.1.3. I8080接口时序

图 9.21 i8080写时序

图 9.22 i8080读时序

CS低有效,处于有效期间才可进行读写操作。

D/C为0,则表示为Command,D/C为1,则表示parameter或者data传输。

WR与RD低有效,进行写操作时,RD需置1,WR由1变0则表示即将进行写操作;

进行读操作时,需先发送一个读命令,随后再进行读取数据,读取数据期间WR需置1,RD由1变0则表示即将进行读操作。

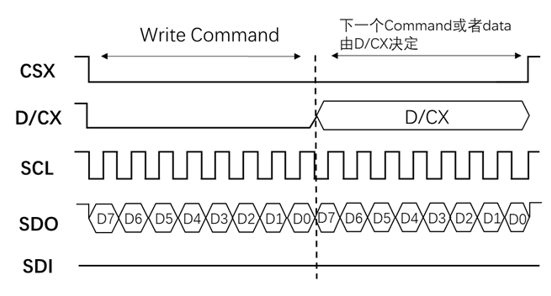

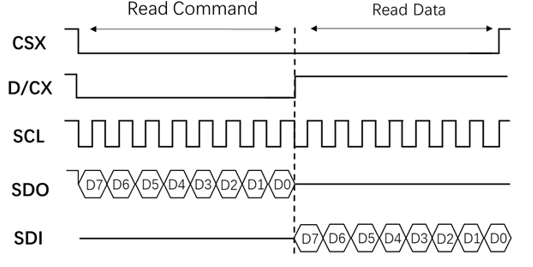

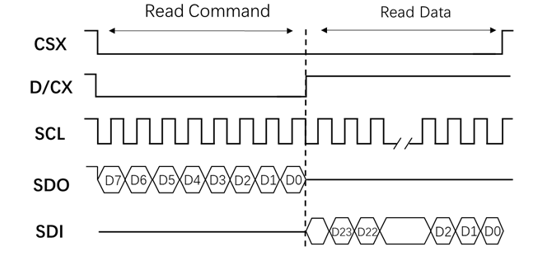

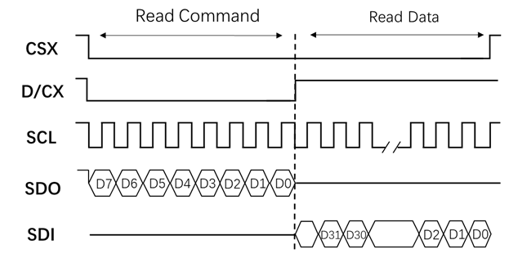

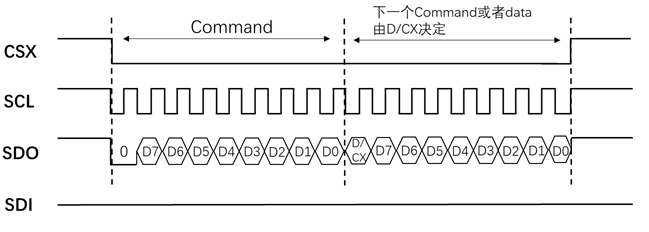

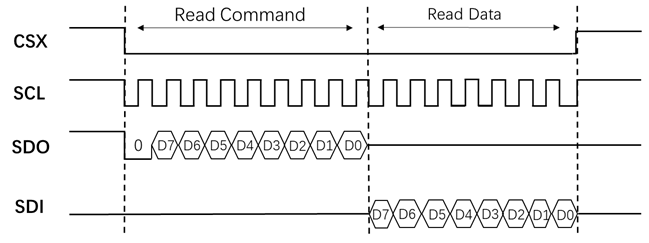

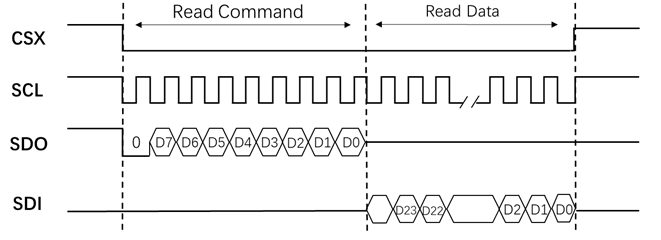

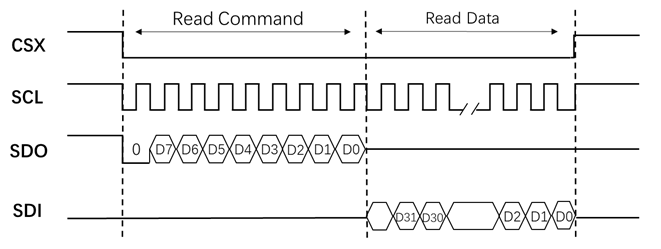

9.4.2.1.4. SPI接口时序

SPI-8BIT 4线模式时序图如下:

图 9.23 spi 4线写时序

图 9.24 spi 4线8bit读时序

图 9.25 spi 4线24bit读时序

图 9.26 spi 4线32bit读时序

SPI-9BIT 3线模式时序图如下:

图 9.27 spi 3线写时序

图 9.28 spi 3线8bit读时序

图 9.29 spi 3线24bit读时序

图 9.30 spi 3线32bit读时序

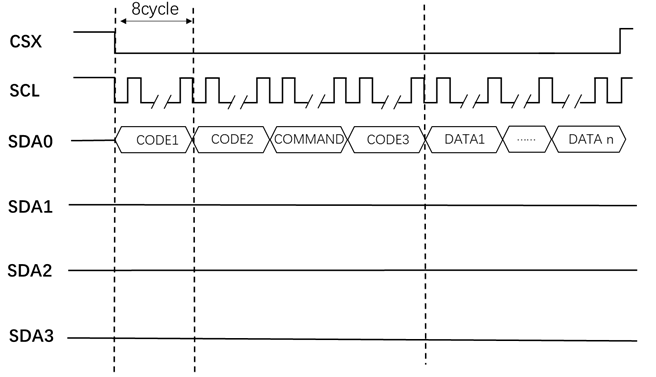

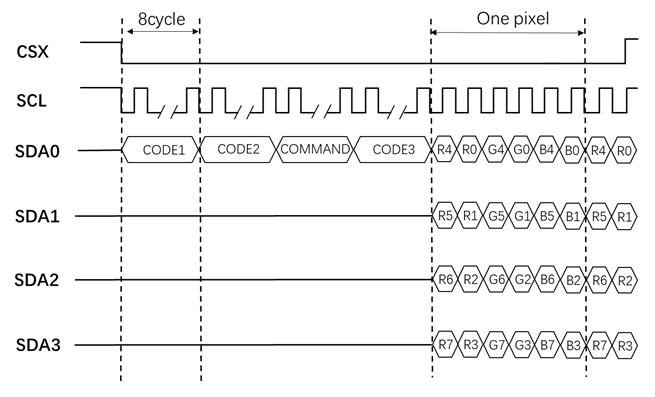

SPI 4-SDA模式时序图如下:

图 9.31 spi 4-sda读写时序

图 9.32 spi 4-sda刷屏时序

其中CODE1/CODE2/CODE3/COMMAND由QSPI_CODE寄存器配置。

刷屏时COMMAND默认为0x2c/0x3c,可通过寄存器修改;

CODE1/CODE2/CODE3需在开始刷屏时前写入

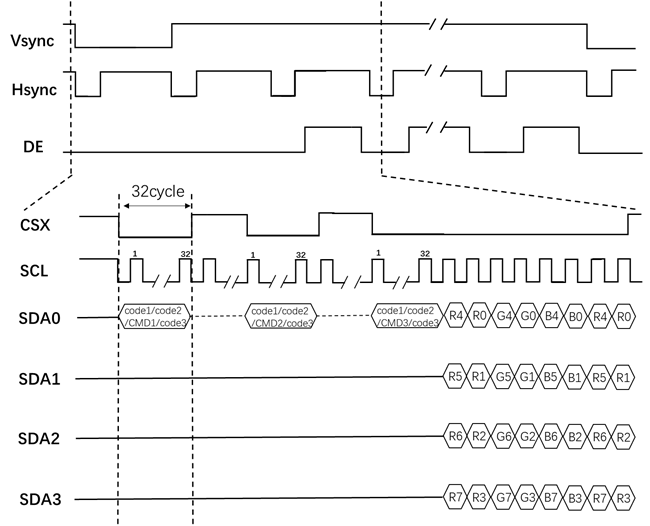

图 9.33 spi 4-sda带时序信息的刷屏时序

其中CMD1即SPI_CMD控制寄存器中的0x2c,表示帧开始;CMD1即SPI_CMD控制寄存器中的0x3c,表示行开始,空白行CS只需持续32个SCL周期,输出空白行信息,注意空白行以及有效行都需要输出引导码CODE1/CODE2/COMMAND/CODE3。

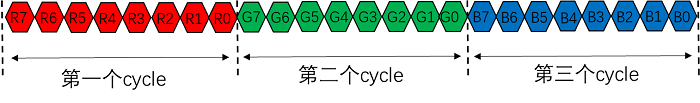

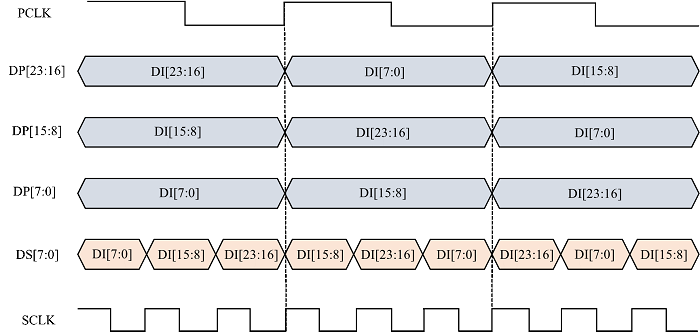

3/4线SPI以及4-sda SPI的数据传输格式支持RGB888、RGB666、RGB565

图 9.34 rgb888格式

图 9.35 rgb666格式

图 9.36 rgb565格式

RGB888转RGB666、RGB565格式,数据舍弃低位,上述示意图表示不同格式的信号出pin排序,比如RGB666中的R5-R0数据实际上对应RGB888中的R7-R2数据,依次类推。

9.4.2.2. 数据块选择以及并转串功能

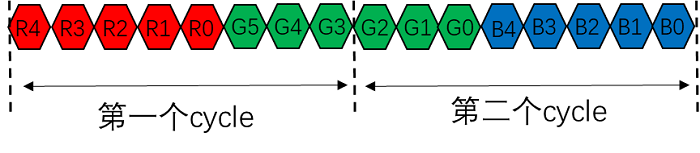

由DE模块输入的DI[23:0]信号进到FMT进行格式转换,输出并行RGB数据DP[23:0]信号,如图 lcd_prgb。

图 9.37 lcd_prgb

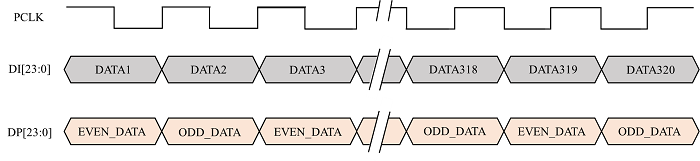

其中DP[23:0]每8位数据可任意互换输出R/G/B信号或者用户设置的data数据,可用于功能调试以及方便layout走线, DP[23:0]再进入到SER0转换成串行RGB数据DS[7:0]信号,如图 lcd_srgb。

图 9.38 lcd_srgb

并行信号转串行信号控制方式:

DE模块输入的完整图片RGB信号DI[23:0]分三组,分别为DI[23:16]、DI[15:8]、DI[7:0]进入FMT转换DP输出,用户可自由配置,例如DP[7:0]可通过配置输出DI[23:16]或者DI[15:8]或者DI[7:0]的数据。

之后三组DP信号进入SER0进行并行转串行,一个PCLK内,DP[7:0]的数据在第一个SCLK cycle给到DS[7:0]; DP[15:8]的数据在第二个SCLK cycle给到DS[7:0]; DP[23:16]的数据在第三个SCLK cycle给到DS[7:0],以此循环。

相关配置寄存器为:LCD_CTL、DATA_SEL、ODD_DATA、EVEN_DATA。

注意无论三组DP信号里存着任何的DI数据,在并行信号转串行信号过程中均为DP[7:0]/ DP[15:8]/ DP[23:16]依次给到DS[7:0]。

9.4.2.3. R/G/B组内数据输出顺序切换功能

组内数据顺序切换:

以8bits为单位进行切换,D23-D16/D15-D8/D7-D0三组。

例如D7-D0组默认输出D7-D6-D5-D4-D3-D2-D1-D0,可切换成顺序D0-D1-D2-D3-D4-D5-D6-D7。用于PCB layout走线可选。

相关配置寄存器为:DATA_SEQ_SEL。

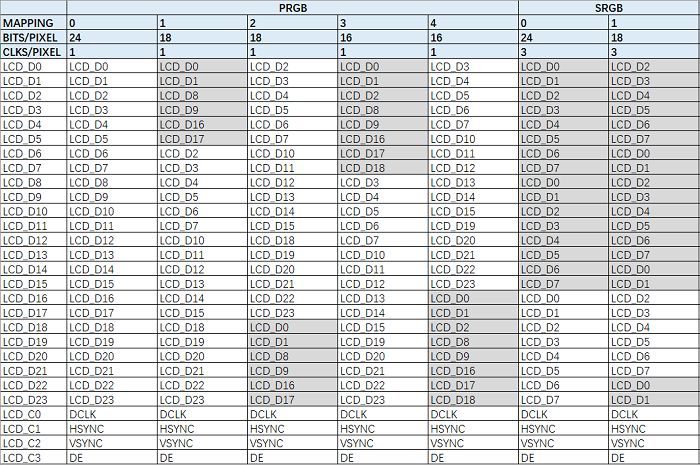

9.4.2.4. PRGB&SRGB模式切换功能

PRGB模式兼容5种输出模式,默认为24bit,可配置为18bit/16bit,其中模式1与模式2可根据应用需求选择。

SRGB模式兼容2种输出模式,默认为8bit,可配置为6bit。

Pin定义如图 lcd_rgb_mode。在某些应用上灰色部分信号无须使用。相关配置寄存器为LCD_CTL。

图 9.39 lcd_rgb_mode

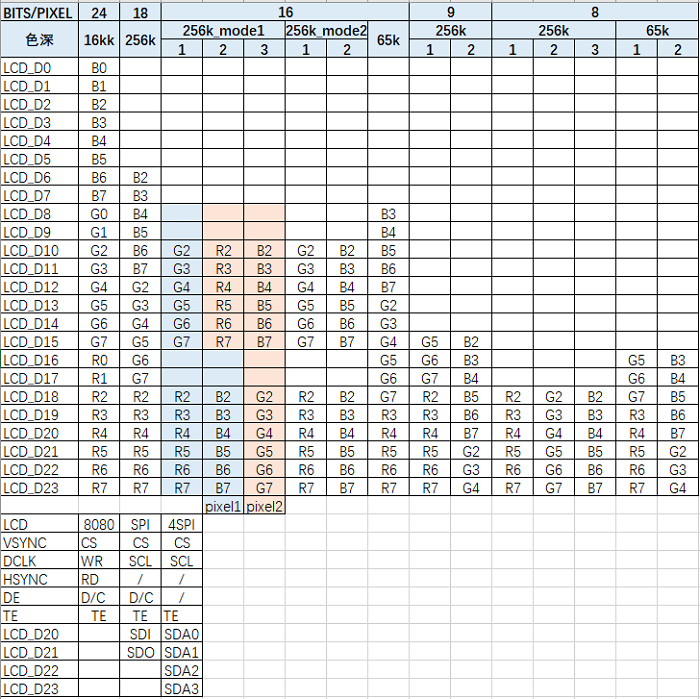

9.4.2.5. I8080模式切换功能

I8080模式兼容8种输出模式。

SPI模式兼容3种输出模式。

Pin定义如图 lcd_i8080_mode。相关配置寄存器为LCD_CTL。

图 9.40 lcd_i8080_mode

9.4.2.6. 像素时钟(pixelclk)与串行时钟(sclk)比例关系

模式

pixelclk : sclk

说明

PRGB

1:4

4倍频作为时钟相位调节,pixel cycle为1:1

SRGB

1:12

4倍频作为时钟相位调节,pixel cycle为1:3(24bit并行转换成8bit串行)

I8080_24BIT

1:10

10倍频作为时钟相位调节,pixel cycle为1:1

I8080_18BIT

1:10

10倍频作为时钟相位调节,pixel cycle为1:1

I8080_16BIT_1

1:15

10倍频作为时钟相位调节,pixel cycle为2:3

I8080_16BIT_2

1:20

10倍频作为时钟相位调节,pixel cycle为1:2

I8080_16BIT_3

1:10

10倍频作为时钟相位调节,pixel cycle为1:1

I8080_9BIT

1:20

10倍频作为时钟相位调节,pixel cycle为1:2

I8080_8BIT_1

1:30

10倍频作为时钟相位调节,pixel cycle为1:3

I8080_8BIT_2

1:20

10倍频作为时钟相位调节,pixel cycle为1:2

4线SPI rgb888

1:96

4倍频作为时钟相位调节,pixel cycle为1:24(24bit并行转换成1bit串行)

4线SPI rgb565

1:64

4倍频作为时钟相位调节,pixel cycle为1:16(16bit并行转换成1bit串行)

3线SPI rgb888

1:108

4倍频作为时钟相位调节,pixel cycle为1:27(24bit并行转换成1bit串行,D/C传输需要消耗3cycle)

3线SPI rgb565

1:72

4倍频作为时钟相位调节,pixel cycle为1:18(16bit并行转换成1bit串行,D/C传输需要消耗2cycle)

4SDA SPI rgb888

1:24

4倍频作为时钟相位调节,pixel cycle为1:6(24bit并行转换成4bit串行)

4SDA SPI rgb565

1:16

4倍频作为时钟相位调节,pixel cycle为1:4(16bit并行转换成4bit串行)