11.2.2. 功能描述

11.2.2.1. 典型应用

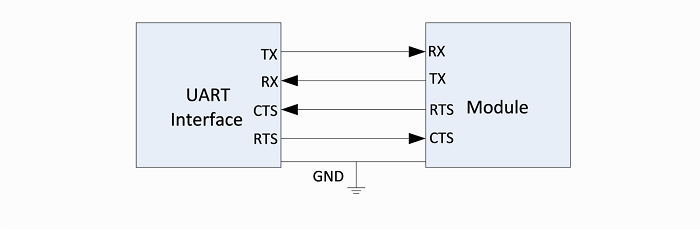

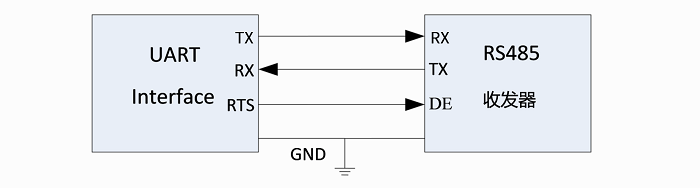

UART典型应用如图所示:

图 11.2 UART 典型应用

11.2.2.2. 功能实现

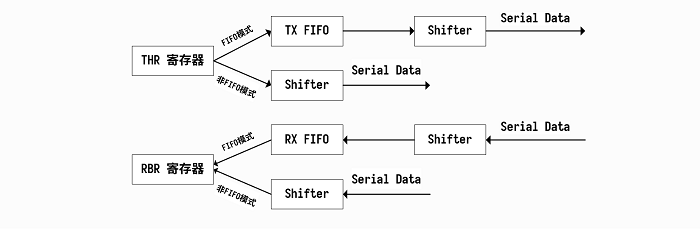

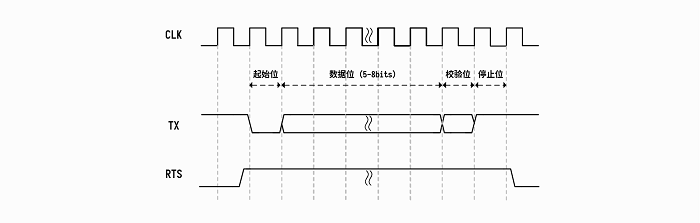

UART时序图

图 11.3 UART 数据流向

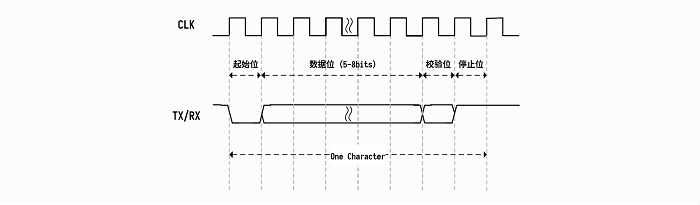

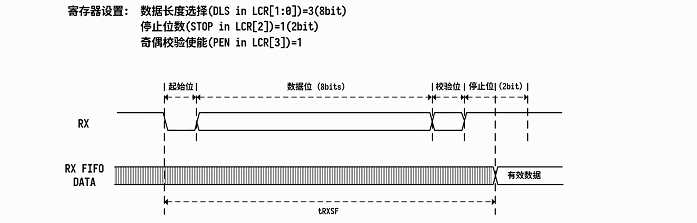

图 11.4 UART 串行数据格式

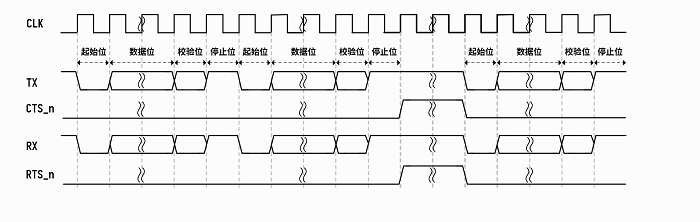

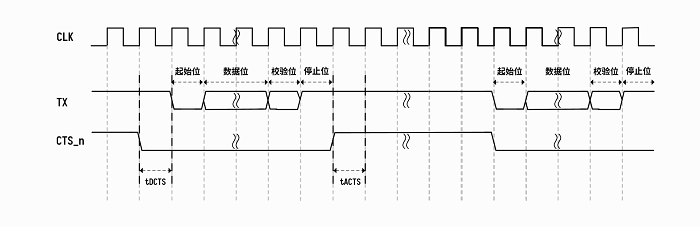

图 11.5 UART 自动流控制时序

图 11.6 UART RS-485时序

UART电气特性

图 11.7 UART 接收时序

Parameter |

Symbol |

Min |

Type |

Max |

Unit |

|---|---|---|---|---|---|

RX start to RX FIFO |

tRXSF |

10.5× BRP(1) |

- |

11× BRP(1) |

ns |

Note : BRP:波特率周期(Baud-Rate Period)

图 11.8 UART nCTS时序

Parameter |

Symbol |

Min |

Type |

Max |

Unit |

|---|---|---|---|---|---|

Delay time of de-asserted nCTS to TX strat |

tDCTS |

- |

- |

BRP(1) |

ns |

Step time of asserted nCTS to stop next transmission |

tACTS |

BRP(1) /4 |

- |

- |

ns |

Note : BRP:波特率周期(Baud-Rate Period)

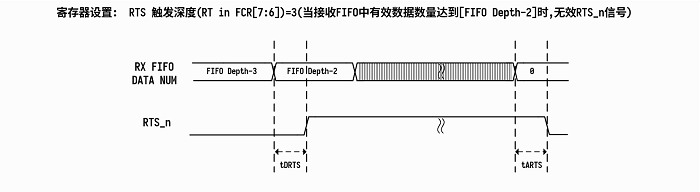

图 11.9 UART nRTS时序

Parameter |

Symbol |

Min |

Type |

Max |

Unit |

|---|---|---|---|---|---|

Delay time of de-asserted nRTS |

tDRTS |

- |

- |

BRP(1) |

ns |

Delay time of asserted nRTS |

tARTS |

- |

- |

BRP(1) |

ns |

Note : BRP:波特率周期(Baud-Rate Period)

11.2.2.3. 操作模式

基础模式设置

寄存器UART_LCR为基本功能的控制寄存器。可配置的基本参数有:数据位宽5-8位,停止位个数1/1.5/2,奇偶校验类型。

UART的一次帧传输主要包括起始信号、数据、校验位和结束信号,低位先传输LSB。

起始信号Start Bit:一个数据帧开始的标志,UART协议规定TX信号出现一个低电平表示一个数据帧的开始;当UART没有传输数据时,保持高电平。

数据信号Data Bit:数据宽度根据不同应用可进行调整,可以配置为5/6/7/8bits数据位宽。

校验位Parity Bit:校验位是1bit纠错信号,校验位包括奇校验、偶校验,同时支持校验位的使能和禁止,可以通过UART_LCR寄存器设置。

结束信号Stop Bit:数据位的停止位,支持1/1.5/2 bit停止位,可以通过UART_LCR寄存器设置。数据帧的结束信号就是把TX拉成高电平。

波特率设置

波特率计算公式:Baudrate = SCLK /(CMU_divisor * 16 * UART_divisor)。SCLK使用PLL_INT1,每个UART通道可单独在CMU配置各自时钟。

CMU_divisor为CMU模块的分频系数。

UART_divisor为UART模块的分频系数,共有16位。寄存器UART_DLL为低8位,寄存器UART_DLH为高8位。时钟源不同频率下,波特率的误差情况,详见CMU功能描述。

DLAB设置

DLAB控制位,即UART_LCR[7],对UART使用比较重要。它是分频系数寄存器的访问控制位。

若DLAB为0,偏移地址0x00为TX/RX FIFO寄存器,偏移地址0x04为IER寄存器。

若DLAB为1,偏移地址0x00为DLL寄存器,偏移地址0x04为DLH寄存器。

UART模块初始化时,需要设置分频系数,先要对DLAB写1,才能访问寄存器DLL和DLH;设置完成后,需对DLAB写0,才能访问寄存器TX/RX FIFO以及IER。

CHCFG_AT_BUSY设置

CHCFG_AT_BUSY(UART_HALT[1])与CHANGE_UPDATE(UART_HALT[2])需要配合使用,来设置UART控制器。它们的作用如下:

CHCFG_AT_BUSY:“忙时配置”使能控制位。使能此位,当UART控制器为busy时,软件也能设置UART控制器,如寄存器LCR(包括DLAB控制位)、DLH、DLL等。

CHANGE_UPDATE:“更新配置”控制位。若“忙时配置”被使能,当对此位写1,即可更新对UART控制器的配置。更新完成后,此位自动清零。

以设置分频系数为例,说明CHCFG_AT_BUSY和CHANGE_UPDATE的配合使用。

首先对CHCFG_AT_BUSY写1,使能“忙时配置”。

再对DLAB写1,并设置DLH和DLL。

最后对CHANGE_UPDATE写1,更新配置。当更新完成时,此位自动清零。

UART繁忙

BUSY标志位,即UART_USR[0],用于表示UART控制器是否繁忙。当TX正在发送数据,或RX正在接受数据,或TX FIFO非空,或RX FIFO非空,BUSY位将会置起,表示UART控制器繁忙。

功能模式设置

UART_FUNCTION(UART_MCR[7:6])为功能模式选择位。

UART_FUNCTION默认为0,配置为基础UART模式。

当UART_FUNCTION为2,配置为RS485模式,即使用UART-TX(RS485-TX)、UART-RX(RS485-RX)、UART-RTS(RS485-DE)三线制通信;

图 11.10 RS485模式,三线制典型应用

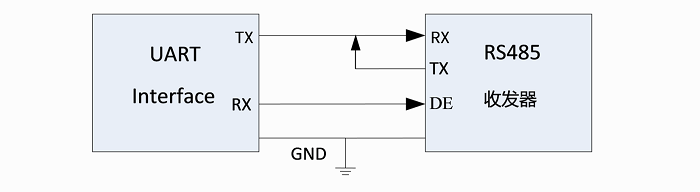

当UART_FUNCTION为3,配置为RS485-2模式,即使用UART-TX(RS485-TX/RX)、UART-RX(RS485-DE)两线制通信。在RS485-2模式中UART-TX既可以发送数据也可以接收数据;UART-RX在模块内部与UART-RTS复用,用于控制DE使能发送。因为RS485为半双工通信,同一时段只能发送或接收,故在此模式中可使用两线制实现RS485通信。

图 11.11 RS485模式,两线制典型应用

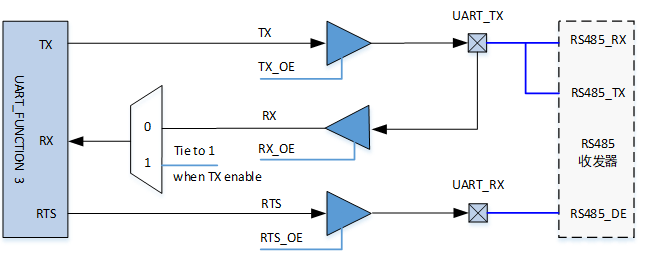

图 11.12 RS485-2模式原理框图

当进入RS485-2模式,RTS复用至UART_RX PIN脚,TX、RX共用UART_TX PIN 脚。TX发送使能时,RX拉高进入空闲状态且RX接收通路关闭。TX发送使能关闭后,开启RX接收通路。数据收发处理逻辑与常规RS485模式类似。

RS485半双工控制

RTS(RS485_DE),在数据发送时输出高电平,需满足以下条件:

软件控制,通过配置MCR[1]=0,DE(rts_n)输出为高电平;

硬件控制,数据开始发送,发送正在进行,发送移位寄存器不为空;

若正在接收数据,必须等待当前数据接收完成。

RTS(RS485_DE),在数据接收时输出低电平,需满足以下条件:

软件控制,通过配置MCR[1]=1,DE(rts_n)输出为低电平;

硬件控制,发送移位寄存器为空且发送FIFO为空,可将RTS输出为低电平状态;

若正在发送数据,必须等待当前数据发送完成。

UART_485_CTL[7](RS485_CTL_MODE,RS485控制模式)

RS485_CTL_MODE = 0:硬件控制模式。DE信号(RTS)在数据发送时通过内部硬件逻辑进行自动控制,发送数据前自动使能DE为有效高电平,当发送移位寄存器为空且发送FIFO为空,则自动切换DE为无效低电平。

RS485_CTL_MODE = 1:软件控制模式。DE信号(RTS)在数据发送时通过外部软件配置进行手动控制,配置MCR[1]=0则DE为有效高电平可发送数据,配置MCR[1]=1则DE为无效低电平可接受数据。

UART_485_DE[3:0](DE_AT,DE有效时间t1)

DE信号上升沿到Sout起始位之间的时间间隔,以串行时钟(sclk)周期为单位。

UART_485_DE[7:4](DE_DAT,DE无效时间t2)

Sout结束位到DE信号下降沿之间的时间间隔,以串行时钟(sclk)周期为单位。