7.1.2. 功能描述

7.1.2.1. PLL

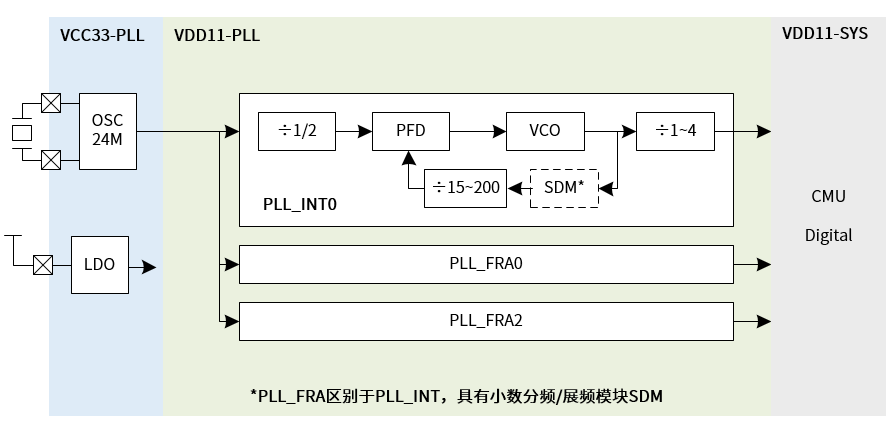

模拟电路PLL用于产生时钟供给整个芯片,总共4个PLL,

PLL内部结构如 图 7.1 所示。

为保证PLL性能要求,PLL_VCO = 24MHz÷(P+1)×(N+1) 频率建议在720MHz~1584MHz之间;

PLL频率计算公式为:PLL_OUT = 24MHz÷(P+1)×(N+1+(F÷(2^17-1)))÷(M+1)。

图 7.1 CMU PLL 内部结构

7.1.2.2. 模块时钟

模块名称 |

总线时钟 |

模块时钟源 |

模块时钟极限频率 |

备注 |

|---|---|---|---|---|

E907 CORE |

- |

PLL_INT0 |

396MHz |

Sign Off 360MHz |

E907 CLIC |

- |

PLL_INT0÷2 |

200MHz |

- |

E907 CLINT |

- |

PLL_INT0÷2 |

200MHz |

- |

E907 DM |

- |

CLK_24M |

24MHz |

- |

AXI |

AXI |

PLL_INT1 |

200MHz |

- |

AHB |

AHB |

PLL_INT1 |

200MHz |

- |

APB0 |

APB0 |

PLL_INT1 |

100MHz |

- |

APB1 |

APB1 |

- |

24MHz |

- |

BROM |

AXI |

- |

- |

- |

SRAM |

AXI |

- |

- |

- |

AHB Matrix |

AHB |

- |

- |

- |

DMA |

AHB |

- |

- |

- |

DCE |

AHB |

- |

- |

- |

XSPI |

AHB |

PLL_FRA0 |

400MHz |

- |

SPI0 |

AHB |

PLL_FRA0 |

100MHz |

- |

SPI1 |

AHB |

PLL_FRA0 |

100MHz |

- |

SDMC0 |

AHB |

PLL_FRA0 |

200MHz |

- |

SDMC1 |

AHB |

PLL_FRA0 |

200MHz |

- |

SYSCFG |

APB0 |

CLK_24M |

24MHz |

- |

CMU |

APB0 |

- |

- |

- |

CMT (SIM) |

APB0 |

- |

- |

- |

SPI_ENC |

APB0 |

HCLK |

- |

- |

AXICFG |

APB0 |

- |

- |

- |

MTOP |

APB0 |

- |

- |

- |

AUDIO |

APB0 |

PLL_INT1 |

26MHz |

- |

GPIO |

APB0 |

- |

- |

- |

PMT (SIM) |

APB0 |

- |

- |

- |

UART0 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART1 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART2 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART3 |

APB0 |

PLL_INT1 |

60MHz |

- |

LCD |

APB0 |

PLL_FRA2 |

400MHz |

DISP_PIXCLK:100MHz |

DE |

APB0 |

PLL_INT1 |

100MHz |

DISP_PIXCLK:100MHz |

GE |

APB0 |

PLL_INT1 |

100MHz |

- |

VE |

TBD |

PLL_INT1 |

200MHz |

- |

WDOG |

APB1 |

CLK_32K |

32KHz |

- |

WRI |

APB1 |

CLK_24M |

24MHz |

- |

SID |

APB1 |

CLK_24M |

24MHz |

- |

RTC |

APB1 |

OSC_32K |

- |

- |

GTC |

APB1 |

- |

- |

- |

I2C0 |

APB1 |

- |

- |

- |

I2C1 |

APB1 |

- |

- |

- |

CAN0 |

APB1 |

- |

- |

- |

CAN1 |

APB1 |

- |

- |

- |

PWM |

APB1 |

CLK_24M |

24MHz |

- |

ADCIM |

APB1 |

CLK_24M |

24MHz |

- |

GPAI |

APB1 |

- |

- |

- |

RTP |

APB1 |

- |

- |

- |

THS |

APB1 |

- |

- |

- |

CIR |

APB1 |

- |

- |

- |

UART在PLL_INT1=588MHz下波特率精度

设定波特率 |

实际波特率 |

波特率偏差 |

CMU除频 |

Over sampling |

Clock source |

UART除频 |

|---|---|---|---|---|---|---|

300 |

300 |

0% |

11 |

16 |

53454545 |

11136 |

600 |

600 |

0% |

11 |

16 |

53454545 |

5568 |

1200 |

1200 |

0% |

11 |

16 |

53454545 |

2784 |

2400 |

2400 |

0% |

11 |

16 |

53454545 |

1392 |

4800 |

4800 |

0% |

11 |

16 |

53454545 |

696 |

9600 |

9600 |

0% |

11 |

16 |

53454545 |

348 |

14400 |

14400 |

0% |

11 |

16 |

53454545 |

232 |

19200 |

19200 |

0% |

11 |

16 |

53454545 |

174 |

38400 |

38401 |

0% |

11 |

16 |

53454545 |

87 |

57600 |

57601 |

0% |

11 |

16 |

53454545 |

58 |

115200 |

115203 |

0% |

11 |

16 |

53454545 |

29 |

230400 |

229687 |

-0.31% |

10 |

16 |

58800000 |

16 |

380400 |

382812 |

0.63% |

12 |

16 |

49000000 |

8 |

460800 |

459375 |

-0.31% |

10 |

16 |

58800000 |

8 |

921600 |

918750 |

-0.31% |

10 |

16 |

58800000 |

4 |

1000000 |

1020833 |

2.08% |

12 |

16 |

49000000 |

3 |

1152000 |

1148437 |

-0.31% |

16 |

16 |

36750000 |

2 |

1500000 |

1531250 |

2.08% |

12 |

16 |

49000000 |

2 |

1750000 |

1750000 |

0% |

7 |

16 |

84000000 |

3 |

2000000 |

2041666 |

2.08% |

9 |

16 |

65333333 |

2 |

2450000 |

2450000 |

0% |

15 |

16 |

39200000 |

1 |

2500000 |

2450000 |

-2% |

15 |

16 |

39200000 |

1 |

3000000 |

3062500 |

2.08% |

12 |

16 |

49000000 |

1 |

AUDIO在PLL_INT1=588MHz下精度

设定频率 |

CMU除频 |

实际频率 |

频率偏差 |

|---|---|---|---|

24.5760MHz |

16 |

24.5000MHz |

0.3% |

22.5792MHz |

17 |

22.6153MHz |

0.1% |

7.1.2.3. 模块开关时序

打开时序:

mod clk 1 -> bus clk 1 -> rst 1

关闭时序:

rst 0 -> bus clk 0 -> mod clk 0