13.2.1. 概述

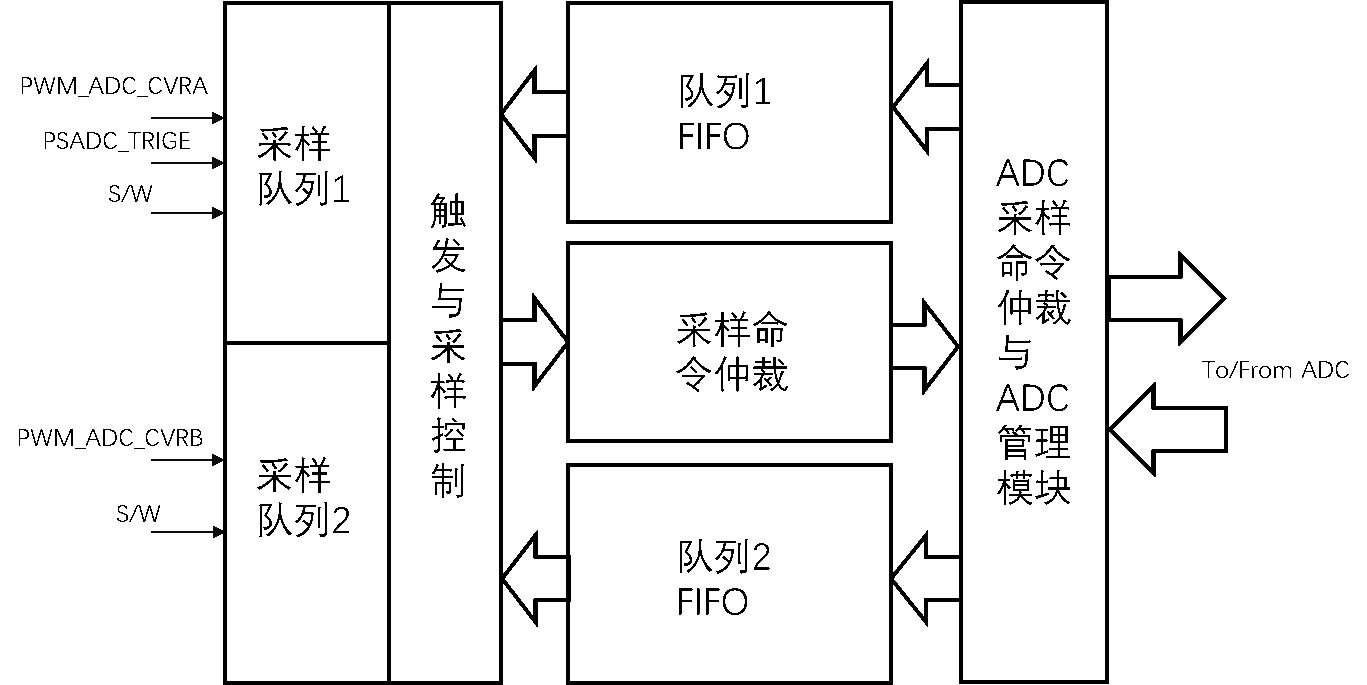

本文档定义了PSADC模块,本模块的功能主要实现了响应PWM控制子系统的捕获信号,对外部模拟信号输入电平 进行采样。配合PWM子系统,通过一个12bits SAR ADC实现对外部电流、电压、以及其他模拟量信号的采样。 本模块实现了两个8个节点的采样队列,既可以各自单独被触发,也可以合并为一个16字节的长队列被一次触发采样。

13.2.1.1. 特性说明

支持APB总线访问寄存器;

最多支持16个模拟信号输入;

支持PWM CVRA/CVRB硬件触发采样;

支持外部信号触发采样;

支持软件触发采样;

支持单次采样与周期采样两种采样模式;

支持双队列模式,和单队列模式;

队列1 FIFO为20*16bits,队列2 FIFO为12*16bits。

13.2.1.2. 原理框图

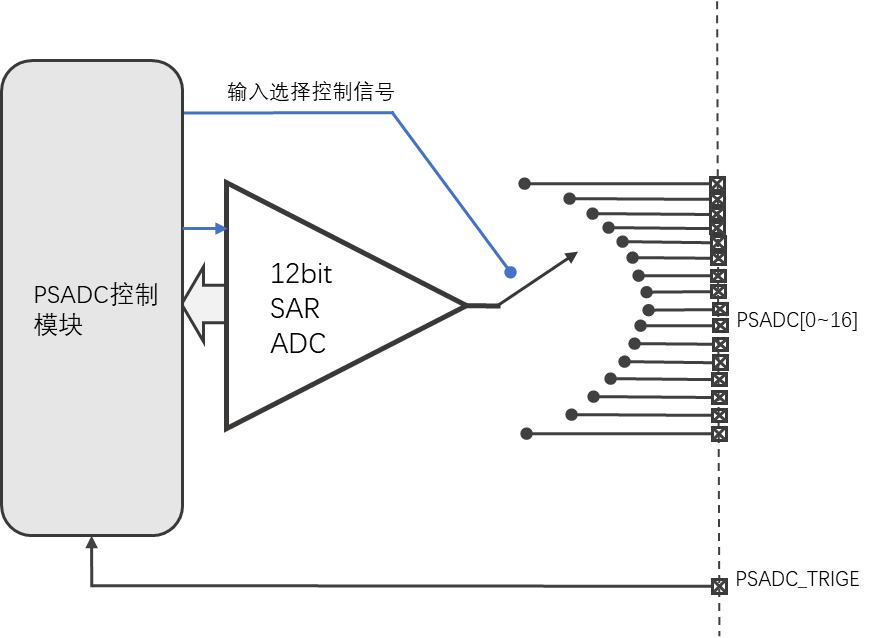

图 13.41 PSADC模块与ADC连接关系

图 13.42 PSADC模块原理图框图