11.1.1. 概述

SPI是一种全双工,同步的串行时钟接口,可以通过中断或DMA方式实现快速的数据传输。SPI控制器包含一个 64字节的接收缓存(RX FIFO)和一个64字节的发送缓存(TX FIFO)。SoC集成2套 QSPI控制器,最大支持4线数据传输,用于SPI NOR/NAND Flash 等存储设备的读写访问。

11.1.1.1. 功能特性

全双工同步串行接口

具有64字节的FIFO缓存用于发送和接收数据

片选信号和时钟的相位和极性可配

支持中断模式或DMA模式

支持四种总线模式:mode0,mode1,mode2和mode3

支持3线或4线的SPI接口

支持可编程串行数据流长度配置:从1bit到32bits

支持标准SPI接口,双路输出/双路输入SPI接口,双路I/O SPI接口,四路输出/四路输入SPI接口,支持 Quad I/O模式和QPI模式;

QSPI0支持AXI直接读取SPI NOR Flash,支持SPI NOR Flash的XiP启动;

QSPI0和QSPI1同时支持引脚重映射,支持12种线序调整方式;

仅QSPI1支持使用控制器内部DMA。

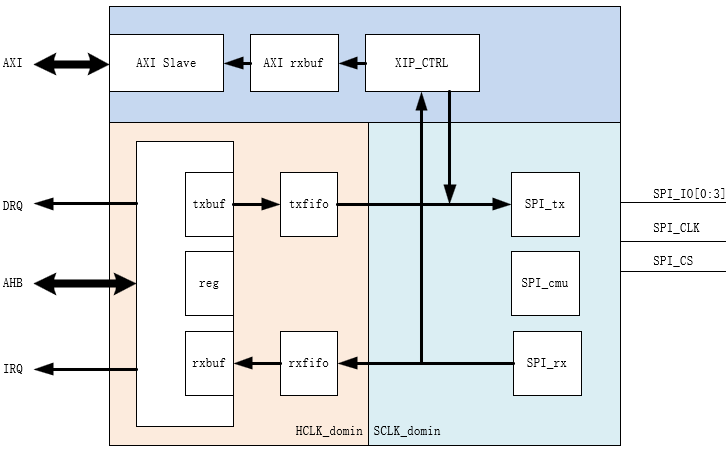

11.1.1.2. 原理框图