2. 原理图设计

2.1. 引脚功能复用

2.1.1. M3A/M3C 功能复用

引脚 |

功能2 |

功能3 |

功能4 |

功能5 |

功能6 |

功能7 |

功能8 |

|---|---|---|---|---|---|---|---|

PA0 |

GPADC0 |

IR_TX |

I2C0_SCL |

UART0_TX |

CPU_NMI |

||

PA1 |

GPADC1 |

IR_RX |

I2C0_SDA |

UART0_RX |

DE_TE |

||

PA2 |

GPADC2 |

CAN1_TX |

I2C1_SCL |

UART1_TX |

UART2_CTS |

||

PA3 |

GPADC3 |

CAN1_RX |

I2C1_SDA |

UART1_RX |

UART2_RTS |

||

PA4 |

GPADC4 |

CAN0_TX |

UART2_TX |

||||

PA5 |

GPADC5 |

CAN0_RX |

UART2_RX |

||||

PA8 |

RTP_XP |

I2C0_SCL |

|||||

PA9 |

RTP_YP |

I2C0_SDA |

|||||

PA10 |

RTP_XN |

IR_RX |

JTAG_MS |

||||

PA11 |

RTP_YN |

IR_TX |

JTAG_CK |

||||

PB0 |

SPI0_WP |

SPI1_WP |

UART0_TX |

||||

PB1 |

SPI0_MISO |

SPI1_MISO |

UART2_TX |

||||

PB2 |

SPI0_CS0 |

SPI1_CS |

UART2_RX |

||||

PB3 |

SPI0_HOLD |

SPI1_HOLD |

UART0_RX |

||||

PB4 |

SPI0_CLK |

SPI1_CLK |

UART2_RTS |

||||

PB5 |

SPI0_MOSI |

SPI1_MOSI |

UART0_RTS |

UART2_CTS |

|||

PB6 |

SDC0_CMD |

SPI1_CS |

UART1_TX |

||||

PB7 |

SDC0_CLK |

SPI1_MISO |

UART1_RX |

||||

PB8 |

SDC0_D3 |

SPI1_MOSI |

UART1_RTS |

UART3_CTS |

|||

PB9 |

SDC0_D0 |

SPI1_CLK |

UART3_RTS |

||||

PB10 |

SDC0_D1 |

SPI1_HOLD |

UART3_TX |

||||

PB11 |

SDC0_D2 |

SPI1_WP |

UART3_RX |

||||

PC0 |

SDC1_D1 |

I2C0_SCL |

UART3_RTS |

JTAG_MS |

|||

PC1 |

SDC1_D0 |

||||||

PC2 |

SDC1_CLK |

UART0_TX |

|||||

PC3 |

SDC1_CMD |

||||||

PC4 |

SDC1_D3 |

PWM0_A |

I2C1_SCL |

UART3_TX |

UART0_RX |

||

PC5 |

SDC1_D2 |

PWM0_B |

I2C1_SDA |

UART3_RX |

JTAG_CK |

||

PC6 |

SDC1_DET |

PWM1_A |

I2C0_SDA |

UART3_CTS |

DE_TE |

IR_RX |

|

PC7 |

PWM1_B |

IR_TX |

|||||

PD0 |

LCD_D0 |

CAN0_TX |

I2C0_SCL |

UART0_TX |

|||

PD1 |

LCD_D1 |

CAN0_RX |

I2C0_SDA |

UART0_RX |

|||

PD2 |

LCD_D2 |

CAN1_TX |

I2C1_SCL |

UART1_TX |

|||

PD3 |

LCD_D3 |

CAN1_RX |

I2C1_SDA |

UART1_RX |

|||

PD4 |

LCD_D4 |

I2C1_SCL |

UART2_TX |

||||

PD5 |

LCD_D5 |

I2C1_SDA |

UART2_RX |

||||

PD6 |

LCD_D6 |

PWM0_A |

DSPK0 |

||||

PD7 |

LCD_D7 |

PWM0_B |

DSPK1 |

||||

PD8 |

LCD_D8 |

PWM1_A |

|||||

PD9 |

LCD_D9 |

||||||

PD10 |

LCD_D10 |

||||||

PD11 |

LCD_D11 |

||||||

PD12 |

LCD_D12 |

||||||

PD13 |

LCD_D13 |

||||||

PD14 |

LCD_D14 |

||||||

PD15 |

LCD_D15 |

||||||

PD16 |

LCD_D16 |

||||||

PD17 |

LCD_D17 |

||||||

PD18 |

LCD_D18 |

||||||

PD19 |

LCD_D19 |

||||||

PD20 |

LCD_D20 |

||||||

PD21 |

LCD_D21 |

||||||

PD22 |

LCD_D22 |

||||||

PD23 |

LCD_D23 |

||||||

PD24 |

LCD_DCLK |

||||||

PD25 |

LCD_HS |

PWM0_B |

|||||

PD26 |

LCD_VS |

PWM1_A |

|||||

PD27 |

LCD_DE |

PWM1_B |

|||||

PE12 |

PWM1_B |

DSPK1 |

|||||

PE13 |

PWM0_A |

DSPK0 |

2.1.2. M3A/M3C QFN68 封装引脚说明

引脚 |

定义 |

类型 |

功能 |

备注说明 |

|---|---|---|---|---|

SYS |

||||

52 |

RESETN |

INPUT |

系统复位 |

内置约30Kohm上拉电阻和去抖滤波,不使用可

直接悬空,若外挂电容建议不超过4.7uF

|

Power |

||||

12,29,54 |

VCC33_IO |

POWER |

CPU IO电压 |

3.3V供电 |

55 |

LDO25 |

POWER |

内置LDO输出 |

内部模拟模块使用,外部接1uf旁路电容 |

28 |

LDO18 |

POWER |

内置LDO输出 |

供内部PSRAM使用,若使用需做好芯片散热,

外部接1uf旁路电容

|

27,53 |

VDD11_SYS |

POWER |

CPU Core电压 |

1.1V供电,若使用内置LDO1x,必须做好芯片散热 |

69 |

GND |

POWER |

- |

GND 铜皮全连接,需多加过孔散热 |

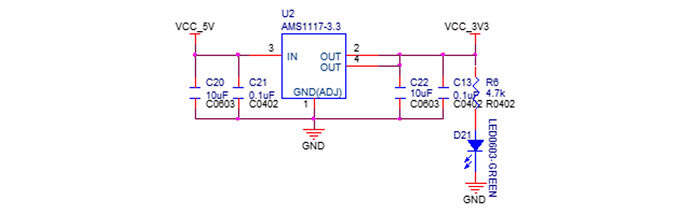

2.2. 时钟和电源

2.2.1. POWER

电源系统

芯片需提供 VCC33_IO(CPU IO 电源:3.3V/100mA),可使用外置LDO或DCDC。

图 2.1 CPU IO 电源 VCC33_IO原理图

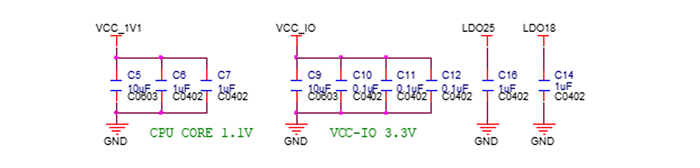

内置LDO18,默认开启,可配置输出1.8V供PSRAM使用,外部接1uF旁路电容即可。

内置LDO1x,默认开启,可配置输出1.1V供VDD11_SYS使用。

内置LDO25,默认开启,供内部模拟模块使用,外部接1uf旁路电容即可。

注意

若使用内置LDO1x,因转换效率问题,功耗会较外置DCDC增加100mW左右。

若使用内置LDO18和LDO1x,芯片表面温度最高43°C左右。

图 2.2 Power 电路去耦电容

上下电时序要求

无上下电时序要求。

内置24M PLL,无需外挂晶振。

复位信号内置约30Kohm上拉电阻和去抖滤波,不使用可直接悬空,若外挂电容建议不超过4.7uF。上电完成后,复位自动释放。

2.2.2. SYS

系统功能脚说明

信号名 |

信号说明 |

应用说明 |

|---|---|---|

UBOOT |

升级模式配置 |

可在UBOOT或bootloader配置任意IO为下拉检测或上拉检测

进入升级模式,默认使用PA0下降沿检测,建议预留按键或跳线

|

RESET |

CPU复位脚 |

内部RC上拉,低电平复位,可悬空,建议预留按键或跳线 |

2.3. 存储

2.3.1. PSRAM

芯片内部默认 Sip 64Mb PSRAM,最高频率 200MHz DDR。

LDO18为芯片内部 1.8V LDO输出,可配置电压为PSRAM供电。

PSRAM 功耗不超过1.8V/50mA。

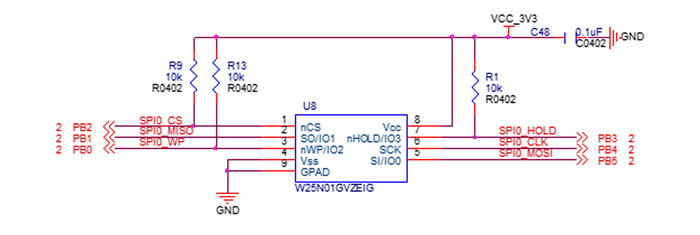

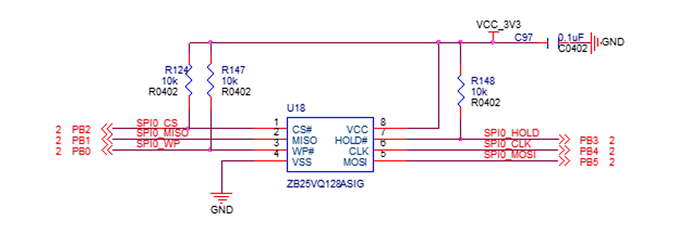

2.3.2. FLASH

SPI0/1 为QSPI控制器,最大支持四线数据传输,用于Flash类型设备的快速读写访问。

默认使用 SPI0 为Flash类型设备启动接口。

QSPI 支持 NAND Flash / NOR Flash,支持单/双/四线模式。

IO最大速率 SDR 100MHz,仅支持3.3V IO电压,Flash容量不限制。

注意

SPI_CS、SPI_WP、SPI_HOLD必需保留上拉电阻。

QSPI 信号必需做等长约束,约束不大于20mil,否则跑四线模式容易出现速度跑不高的情况。

图 2.3 SPI0 NAND Flash电路原理图

图 2.4 SPI0 NOR Flash电路原理图

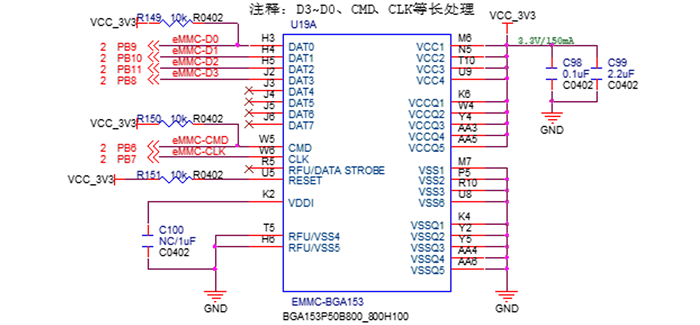

2.3.3. eMMC

使用SDC0接口,支持单线/四线模式,支持eMMC 4.41协议,支持SDR25/SDR50/DDR50模式。

IO最大速率 DDR 50MHz,仅支持3.3V IO电压。

D0、CMD和RST信号建议上拉到VCC33_IO。

注意

SDC0_D0~SDC0_D3、SDC0_CLK、SDC0_CMD信号走线做等长约束,约束不大于50mil。

CLK信号不需上拉,最好在靠近主控端串联22欧电阻,若并联容值不超过22pF。

图 2.5 SDC0 eMMC电路原理图

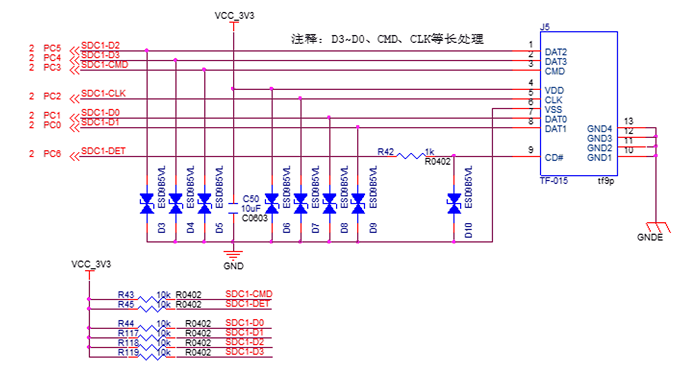

2.3.4. CARD

使用SDC1接口,支持单线/四线模式。

IO最大速率 DDR 50MHz,仅支持3.3V IO电压。

CLK信号不需上拉,最好在靠近主控端串联22欧电阻,若并联容值不超过22pF。

D0、CMD和DET信号建议上拉到VCC33_IO。

SD接口信号线TVS管结电容 < 22pF,否则影响信号传输质量。

建议保留DET信号线上的1k串联电阻,避免在插入SD CARD时产生信号下冲,同时提高GPIO ESD性能。

注意

SDC1_D0~SDC1_D3、SDC1_CLK、SDC1_CMD信号走线做等长约束,约束不大于50mil。

CLK信号不需上拉,最好在靠近主控端串联22欧电阻,若并联容值不超过22pF。

图 2.6 SDC1 CARD电路原理图

2.4. 多媒体

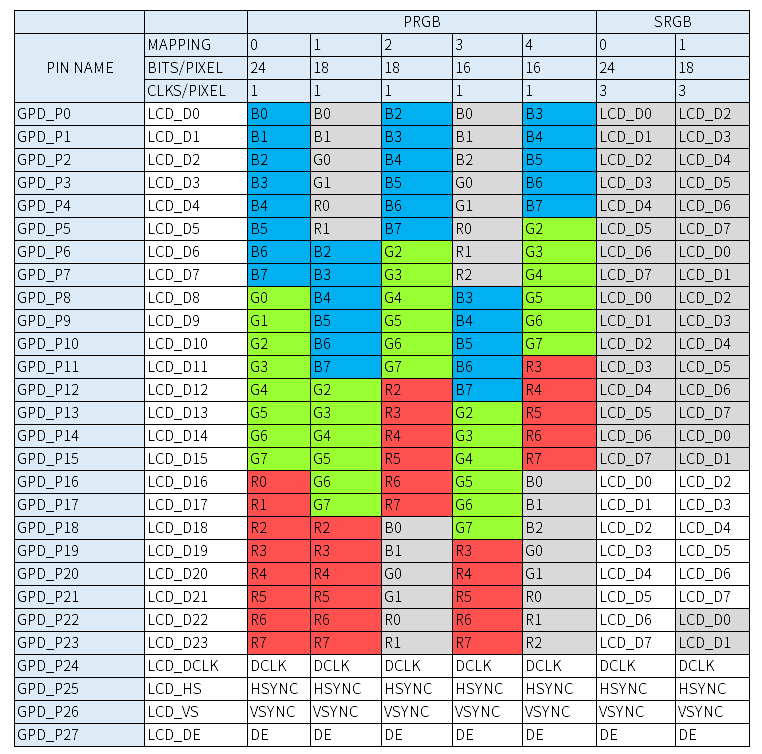

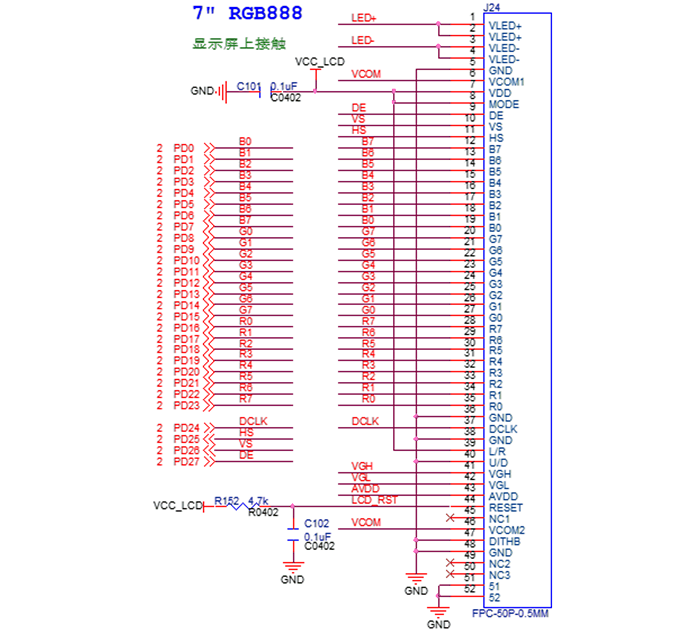

2.4.1. PRGB屏接口

PRGB模式兼容5种MAPPING输出配置,默认为24bits,可配置为18bits、16bits,相应的低位不使用。

配置0:RGB888建议使用,支持R/G/B 整组信号互换。

配置1:RGB666建议使用,支持R/G/B 整组信号互换。

配置2:RGB666,支持R/G/B 整组信号互换。

配置3:RGB565建议使用,支持R/G/B 整组信号互换。

配置4:RGB565,支持R/G/B 整组信号互换。

注意

支持组内信号高位到低位排序互换,需软件配置data-mirror。

默认配置为RGB,为方便Layout,可将R和B整组互换,需软件配置将data-order修改为BGR。

RGB888接口高位可用于RGB666或565,CPU端相应的低位不接或可用于其他功能。

图 2.7 RGB 不同配置定义

图 2.8 RGB565 / RGB666 电路原理图

图 2.9 RGB888 电路原理图

2.4.2. MCU屏接口

MCU屏接口包含常见的I8080、SPI、QSPI。

图 2.10 I8080 不同配置定义

注意

注意SPI屏通信接口交叉,PD21/SDO为输出,需接屏端SDI输入;PD20/SDI为输入,需接屏端SDO输出。

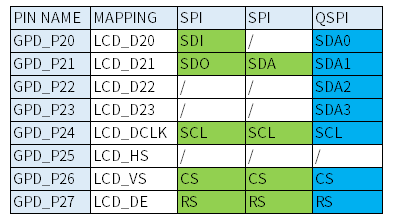

图 2.11 SPI/QSPI屏连接定义

2.4.3. TP

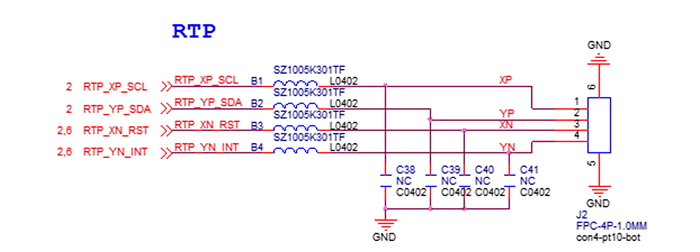

集成 RTP 电阻触摸屏接口,可支持RTP电阻屏触摸。

RTP 仅支持4线,即X+/X-/Y+/Y-。

RTP 支持最多2点触摸。

图 2.12 RTP 电阻屏触摸电路原理图

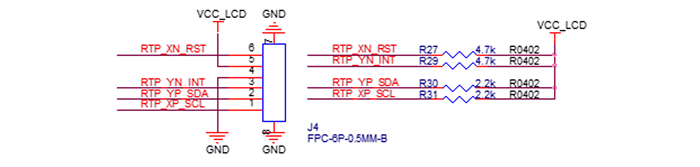

使用I2C和GPIO,可支持CTP电容屏触摸。

图 2.13 CTP 电容屏触摸电路原理图

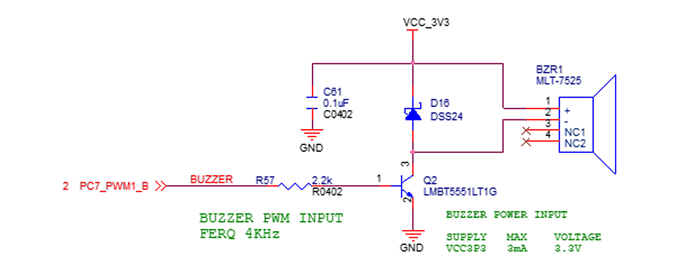

2.4.4. PWM

支持PWM0~PWM2共两组PWM波形发生器

PWMx_A和PWMx_B同属一组PWM,可配置成单独输出或同时输出,但频率相同,占空比可不相同。

PWM通常用于背光控制,频率一般为20kHz~1MHz。

PWM通常用于蜂鸣器,频率一般为3kHz~4kHz。

注意

PWMx_A和PWMx_B可分开独立控制,但频率是相同的,占空比可独立调。

不同频率的应用不能使用同一组PWM,比如蜂鸣器和背光,需分开使用不同通道。

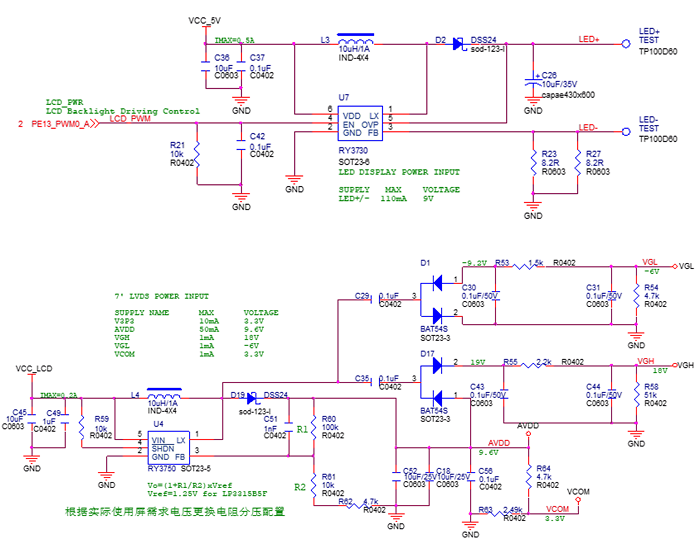

图 2.14 LCD 背光和偏压电路原理图

图 2.15 蜂鸣器电路原理图

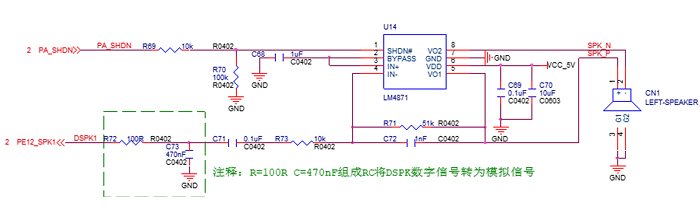

2.4.5. AUDIO

Speaker

支持2路单端输出(双喇叭,左右声道输出)。

支持1路差分输出(单喇叭,单声道输出)。

支持DSPK0和DSPK1内部混音后,再通过任意单一通路输出。

注意

DSPK是数字信号,从CPU出来必需接RC(R=100R,C=470nF)转换成模拟信号才能给到音频功放。

图 2.16 Speaker 单端输出电路原理图

2.5. 通用接口

2.5.1. SPI

SPI0/1 为标准SPI控制器,用于存储设备或其他SPI接口设备的访问。

支持Master和Slave。

支持QSPI 单/双/四线模式。

SPI_CS、SPI_WP、SPI_HOLD必需保留上拉电阻。

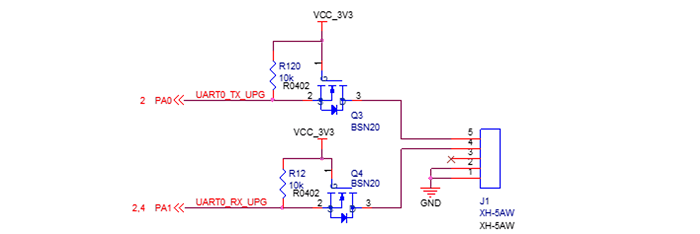

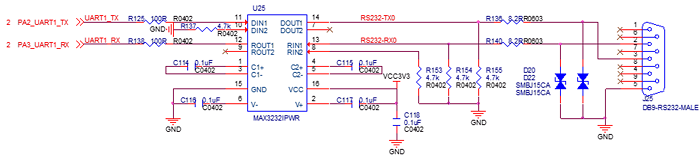

2.5.2. UART

UART兼容工业16550标准,支持常用波特率,最大波特率支持5Mbps。

支持UART 两线(TX、RX),通常应用于TTL、RS485、RS232、DEBUG打印。

支持UART 三线(TX、RX、RTS),通常应用于RS485、某些模块比如RTL8723DS其蓝牙只需UART三线。

支持UART 四线自动流控(TX、RX、RTS、CTS),通常应用于RS232、蓝牙通信。

图 2.17 串口烧录电路原理图

图 2.18 RS232串口电路原理图

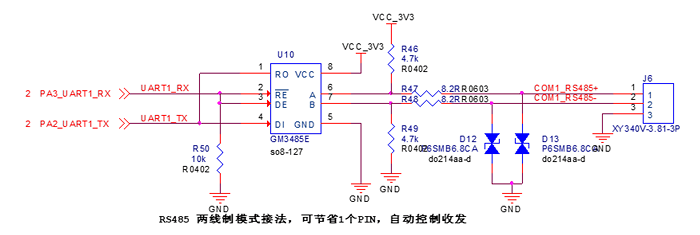

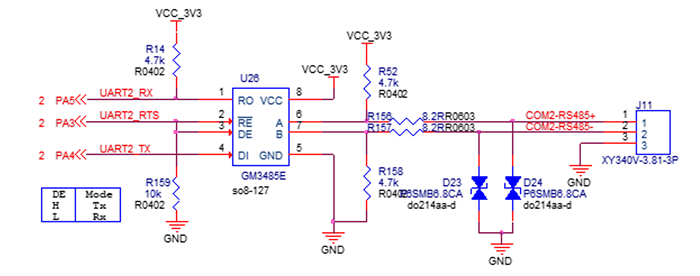

RS485支持硬件自动控制收发方向,也支持软件控制收发方向

在IO资源紧张时,建议采用两线接法,通过UART_TX引脚进行半双工收发,UART_RX引脚进行自动方向控制。

需要做光耦隔离时,可采用常规三线接法,UART_RTS引脚进行自动方向控制。

注意

使用两线接法时,TX引脚既当发送又当接收;RX引脚用于自动控制收发方向。

使用三线接法时,建议使用UART_RTS接485-DIR,方便使用硬件自动控制收发功能。

图 2.19 RS485 两线接法电路原理图

图 2.20 RS485 三线接法电路原理图

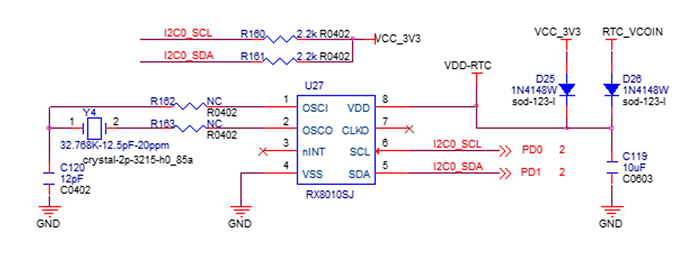

2.5.3. I2C

I2C速率最大支持400kbps,支持master 和 slave 模式。

图 2.21 I2C 外接RTC电路原理图

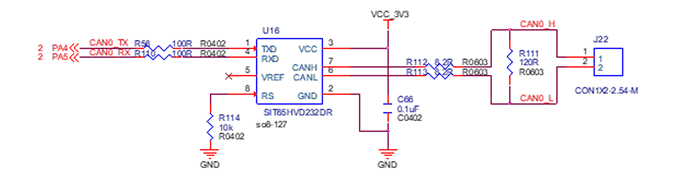

2.5.4. CAN

支持CAN0和CAN1两套控制器

支持CAN2.0A和CAN2.0B协议,可编程通信速率最高1Mbps。

外围电路需接收发器,才能组成CAN总线网络。

图 2.22 CAN 电路原理图

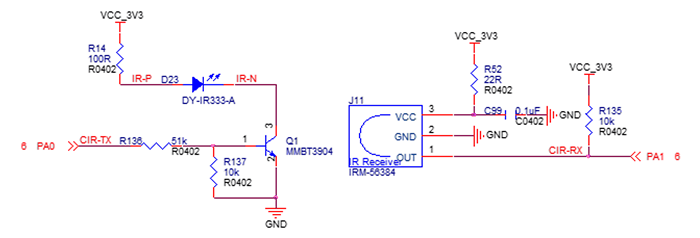

2.5.5. CIR

支持市面常见红外协议,如NEC、RC5、RC6、RC-MM、Sony、Sanyo、JVC等。

图 2.23 CIR 红外收发电路原理图

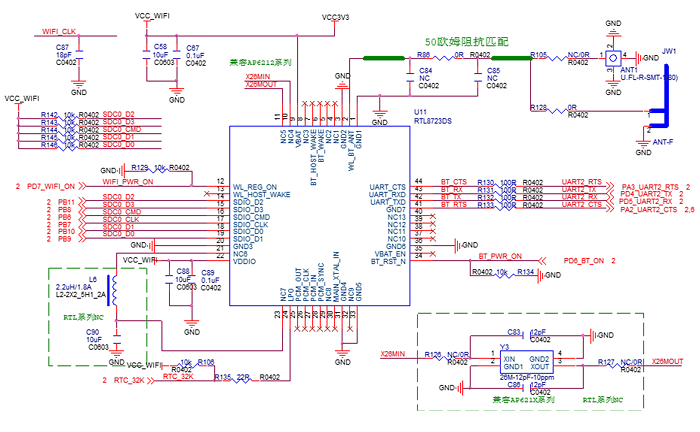

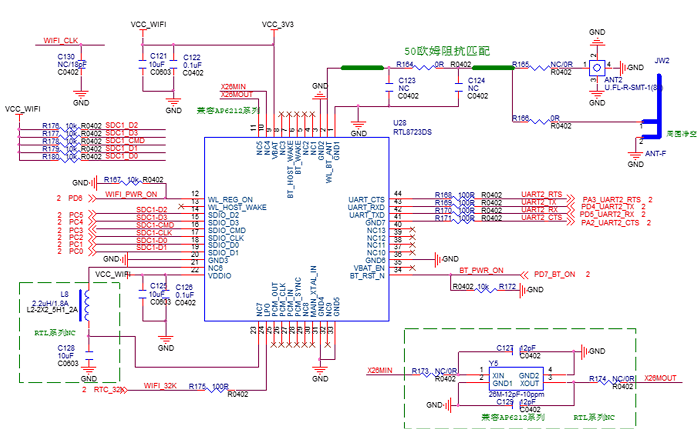

2.5.6. SDIO

SDC0/SDC1 可用于用于访问SDIO接口的设备,比如eMMC、CARD、WiFi模组。

SDIO 接口只支持 3.3V IO 电平,接口顺序关系需注意。

SDIO 接口按等长约束走线,CLOCK 尽量包地处理。

天线端增加 TVS 管,防止 ESD 静电打坏模块。

所有电源滤波电容尽量靠近芯片电源输入脚放置。

图 2.24 SDC0 WiFi+BT 电路原理图

图 2.25 SDC1 WiFi+BT 电路原理图