9.5.2. 功能描述

9.5.2.1. 功能实现

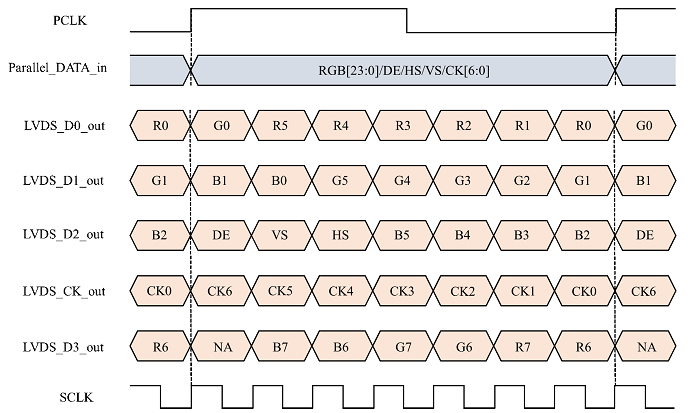

由DE模块输入的DI[23:0]、DE/HS/VS/CK信号(其中差分CK信号由寄存器配置,使用默认值即可)进到2C1处理输出信号选择DATA[34:0],这里控制差分输出LVDS[4:0],图 lvds_format。

并行信号转换为差分信号格式:需要两个不同时钟控制,串行时钟SCLK的频率为并行时钟PCLK的7倍。

SCLK的第一个cycle,并行信号的G0/B1/DE/CK6/NA分别给到LVDS_D0/ LVDS_D1/ LVDS_D2/ LVDS_CK/ LVDS_D3的第一位;

SCLK的第二个cycle,并行信号的R5/B0/VS/CK5/NA给到LVDS_D0/ LVDS_D1/ LVDS_D2/ LVDS_CK/ LVDS_D3第二位;

以此类推进行7个SCLK cycle数据转换,等到下一个PCLK cycle到达,并行信号同时更新,LVDS信号按照同样的方式转换。

图 9.38 lvds_format

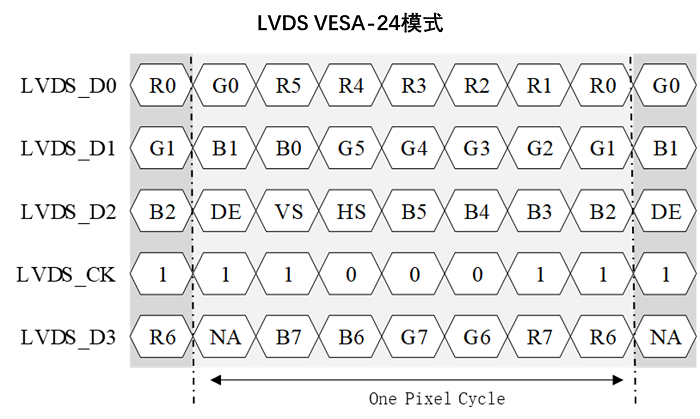

9.5.2.2. VESA-24模式时序(也称NS模式)

图 9.39 lvds_vesa-24(ns)

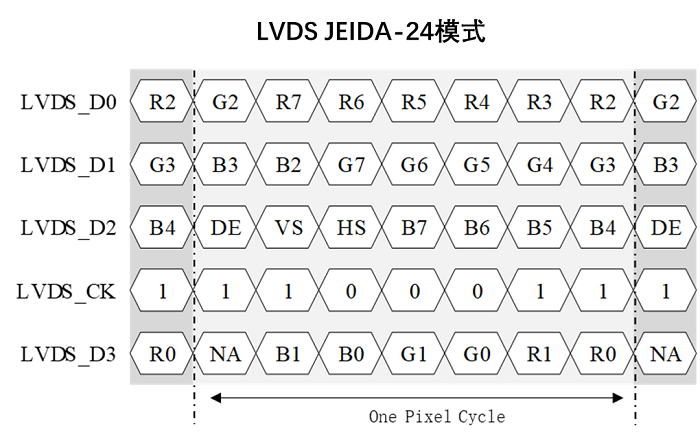

9.5.2.3. JEIDA模式时序

图 9.40 lvds_jeida-24

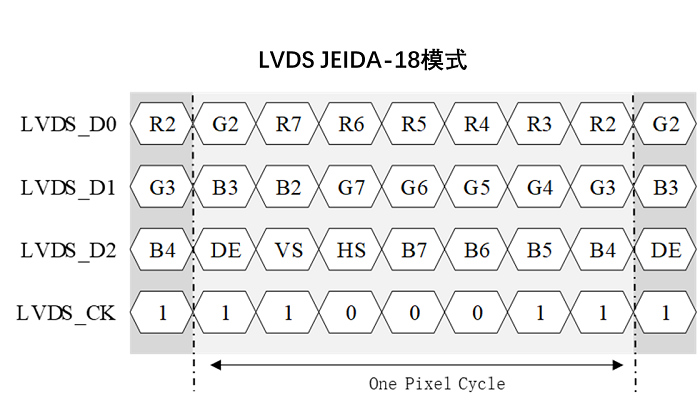

图 9.41 lvds_jeida-18

其中R7-R2对应6bit屏信号的R5-R0;G7-G2对应6bit屏信号的G5-G0;B7-B2对应6bit屏信号的B5-B0;