2. 原理图设计

2.1. 管脚说明和功能复用

2.1.1. QFN88 管脚和功能复用

管脚 |

定义 |

类型 |

功能 |

备注说明 |

|---|---|---|---|---|

RTC |

||||

83 |

RTC_IO |

OD |

RTC唤醒

32K时钟输出

|

OD输出,外部需上拉电阻,上拉电压不能超过5V |

84 |

RTC_VCOIN |

POWER |

- |

若不考虑掉电保持可悬空,内部有二极管从3.3V取电 |

85 |

RTC_XO |

OUTPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

86 |

RTC_XI |

INPUT |

- |

接32.768kHz无源晶振,若不使用RTC功能可悬空 |

SYS |

||||

67 |

RESET |

INPUT |

系统复位 |

内置约30Kohm上拉电阻和去抖滤波,不使用可

直接悬空,若外挂电容建议不超过4.7uF

|

81 |

PLL_XO |

OUTPUT |

- |

接24MHz无源晶振 |

82 |

PLL_XI |

INPUT |

- |

接24MHz无源晶振 |

Power |

||||

15,36,69 |

VCC33_IO |

POWER |

CPU IO电压 |

3.3V供电 |

70 |

LDO25 |

POWER |

内置LDO输出 |

内部模拟模块使用,外部接1uf旁路电容 |

31 |

LDO18 |

POWER |

内置LDO输出 |

供内部PSRAM使用,若使用需做好芯片散热,

外部接1uf旁路电容

|

8,30,68 |

VDD11_SYS |

POWER |

CPU Core电压 |

1.1V供电,若使用内置LDO1x,必须做好芯片散热 |

89 |

GND |

POWER |

地焊盘 |

建议多加VIA加强散热 |

管脚 |

功能1 |

功能2 |

功能3 |

功能4 |

功能5 |

功能6 |

功能8 |

|---|---|---|---|---|---|---|---|

GPIO A |

|||||||

71 |

PA0 |

GPADC0 |

IR_TX |

I2C0_SCL |

UART0_TX |

CPU_NMI |

|

72 |

PA1 |

GPADC1 |

IR_RX |

I2C0_SDA |

UART0_RX |

DE_TE |

|

73 |

PA2 |

GPADC2 |

I2C1_SCL |

UART1_TX |

UART2_CTS |

||

74 |

PA3 |

GPADC3 |

I2C1_SDA |

UART1_RX |

UART2_RTS |

||

75 |

PA4 |

GPADC4 |

CAN0_TX |

UART2_TX |

|||

76 |

PA5 |

GPADC5 |

CAN0_RX |

UART2_RX |

RTC_32K |

||

77 |

PA8 |

RTP_XP |

I2C2_SCL |

||||

78 |

PA9 |

RTP_YP |

I2C2_SDA |

||||

79 |

PA10 |

RTP_XN |

IR_RX |

JTAG_MS |

|||

80 |

PA11 |

RTP_YN |

IR_TX |

JTAG_CK |

|||

GPIO B |

|||||||

55 |

PB0 |

SPI0_WP |

SPI1_WP |

UART4_TX |

|||

56 |

PB1 |

SPI0_MISO |

SPI1_MISO |

UART6_TX |

|||

57 |

PB2 |

SPI0_CS0 |

SPI1_CS |

UART6_RX |

|||

58 |

PB3 |

SPI0_HOLD |

SPI1_HOLD |

UART4_RX |

|||

59 |

PB4 |

SPI0_CLK |

SPI1_CLK |

UART6_RTS |

|||

60 |

PB5 |

SPI0_MOSI |

SPI1_MOSI |

UART4_RTS |

UART6_CTS |

||

61 |

PB6 |

SDC0_CMD |

SPI2_CS |

UART5_TX |

FLASH_CS |

||

62 |

PB7 |

SDC0_CLK |

SPI2_MISO |

UART5_RX |

FLASH_MISO |

||

63 |

PB8 |

SDC0_D3 |

SPI2_MOSI |

UART5_RTS |

UART7_CTS |

FLASH_MOSI |

|

64 |

PB9 |

SDC0_D0 |

SPI2_CLK |

UART7_RTS |

FLASH_CLK |

||

65 |

PB10 |

SDC0_D1 |

SPI2_HOLD |

UART7_TX |

|||

66 |

PB11 |

SDC0_D2 |

SPI2_WP |

SPI0_CS1 |

UART7_RX |

||

GPIO C |

|||||||

1 |

PC0 |

SDC1_D1 |

I2C2_SCL |

UART3_RTS |

JTAG_MS |

||

2 |

PC1 |

SDC1_D0 |

|||||

3 |

PC2 |

SDC1_CLK |

UART0_TX |

||||

4 |

PC3 |

SDC1_CMD |

|||||

5 |

PC4 |

SDC1_D3 |

I2C1_SCL |

UART3_TX |

UART0_RX |

||

6 |

PC5 |

SDC1_D2 |

I2C1_SDA |

UART3_RX |

JTAG_CK |

||

7 |

PC6 |

SDC1_DET |

I2C2_SDA |

UART3_CTS |

DE_TE |

||

GPIO D |

|||||||

40 |

PD0 |

LCD_D0 |

SPI3_CLK |

I2C0_SCL |

UART0_TX |

PBUS_AD0 |

|

39 |

PD1 |

LCD_D1 |

SPI3_CS |

I2C0_SDA |

UART0_RX |

PBUS_AD1 |

|

38 |

PD2 |

LCD_D2 |

SPI3_MOSI |

I2C1_SCL |

UART1_TX |

PBUS_AD2 |

|

37 |

PD3 |

LCD_D3 |

SPI3_MISO |

I2C1_SDA |

UART1_RX |

PBUS_AD3 |

|

35 |

PD4 |

LCD_D4 |

SPI1_CS |

I2C2_SCL |

UART2_TX |

PBUS_AD4 |

|

34 |

PD5 |

LCD_D5 |

SPI1_MISO |

I2C2_SDA |

UART2_RX |

PBUS_AD5 |

|

33 |

PD6 |

LCD_D6 |

SPI1_MOSI |

PWM0_A |

DSPK0 |

PBUS_AD6 |

|

32 |

PD7 |

LCD_D7 |

SPI1_CLK |

PWM0_B |

DSPK1 |

PBUS_AD7 |

|

29 |

PD8 |

LCD_D8 |

SPI1_HOLD |

PWM1_A |

PBUS_CLK |

||

28 |

PD9 |

LCD_D9 |

SPI1_WP |

PBUS_NCS |

|||

27 |

PD10 |

LCD_D10 |

PBUS_NADV |

||||

26 |

PD11 |

LCD_D11 |

I2S_DIN |

PBUS_NWE |

|||

25 |

PD12 |

LCD_D12 |

I2S_DOUT |

PBUS_NOE |

|||

24 |

PD13 |

LCD_D13 |

I2S_LRCK |

CLK_OUT0 |

|||

23 |

PD14 |

LCD_D14 |

I2S_BCLK |

PBUS_AD8 |

|||

22 |

PD15 |

LCD_D15 |

I2S_MCLK |

PBUS_AD9 |

|||

21 |

PD16 |

LCD_D16 |

PWM1_B |

DMIC_CLK |

UART2_TX |

PBUS_AD10 |

|

20 |

PD17 |

LCD_D17 |

PWM2_A |

DMIC_D0 |

UART2_RX |

PBUS_AD11 |

|

19 |

PD18 |

LCD_D18 |

LVDS_D0N |

DSI_D0N |

PBUS_AD12 |

||

18 |

PD19 |

LCD_D19 |

LVDS_D0P |

DSI_D0P |

PBUS_AD13 |

||

17 |

PD20 |

LCD_D20 |

LVDS_D1N |

DSI_D1N |

PBUS_AD14 |

||

16 |

PD21 |

LCD_D21 |

LVDS_D1P |

DSI_D1P |

PBUS_AD15 |

||

14 |

PD22 |

LCD_D22 |

LVDS_D2N |

DSI_CKN |

|||

13 |

PD23 |

LCD_D23 |

LVDS_D2P |

DSI_CKP |

|||

12 |

PD24 |

LCD_DCLK |

LVDS_CKN |

DSI_D2N |

|||

11 |

PD25 |

LCD_HS |

LVDS_CKP |

DSI_D2P |

PWM2_B |

||

10 |

PD26 |

LCD_VS |

LVDS_D3N |

DSI_D3N |

PWM3_A |

||

9 |

PD27 |

LCD_DE |

LVDS_D3P |

DSI_D3P |

PWM3_B |

CMU_CKT |

|

GPIO E |

|||||||

41 |

PE0 |

EMAC_RXD1 |

DVP_D0 |

PWM0_A |

UART3_TX |

||

42 |

PE1 |

EMAC_RXD0 |

DVP_D1 |

PWM0_B |

UART3_RX |

||

43 |

PE2 |

EMAC_RXCTL |

DVP_D2 |

UART4_TX |

|||

44 |

PE3 |

EMAC_CLKIN |

DVP_D3 |

I2S_MCLK |

UART4_RX |

||

45 |

PE4 |

EMAC_TXD1 |

DVP_D4 |

UART5_TX |

|||

46 |

PE5 |

EMAC_TXD0 |

DVP_D5 |

UART5_RX |

|||

47 |

PE6 |

EMAC_TXCK |

DVP_D6 |

UART6_TX |

|||

48 |

PE7 |

EMAC_TXCTL |

DVP_D7 |

UART6_RX |

|||

49 |

PE8 |

EMAC_MDC |

DVP_CK |

UART7_TX |

|||

50 |

PE9 |

EMAC_MDIO |

DVP_HS |

UART7_RX |

|||

51 |

PE10 |

CLK_OUT2 |

DVP_VS |

I2S_DIN |

DMIC_CLK |

||

52 |

PE11 |

CLK_OUT1 |

PWM1_A |

I2S_LRCK |

DMIC_D0 |

||

53 |

PE12 |

SPI2_CLK |

PWM1_B |

I2S_BCLK |

DSPK1 |

||

54 |

PE13 |

SPI2_CS |

PWM2_A |

I2S_DOUT |

DSPK0 |

||

USB |

|||||||

87 |

PU0 |

USB_DM |

UART0_RX |

UART1_RX |

|||

88 |

PU1 |

USB_DP |

UART0_TX |

UART1_TX |

|||

2.2. 时钟和电源

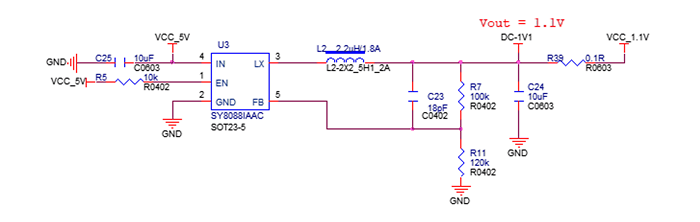

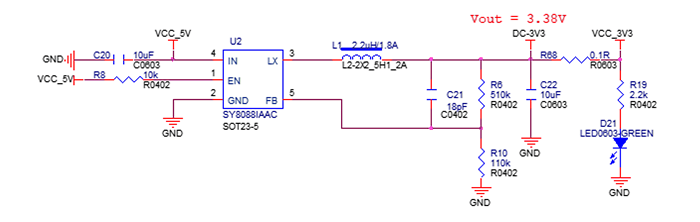

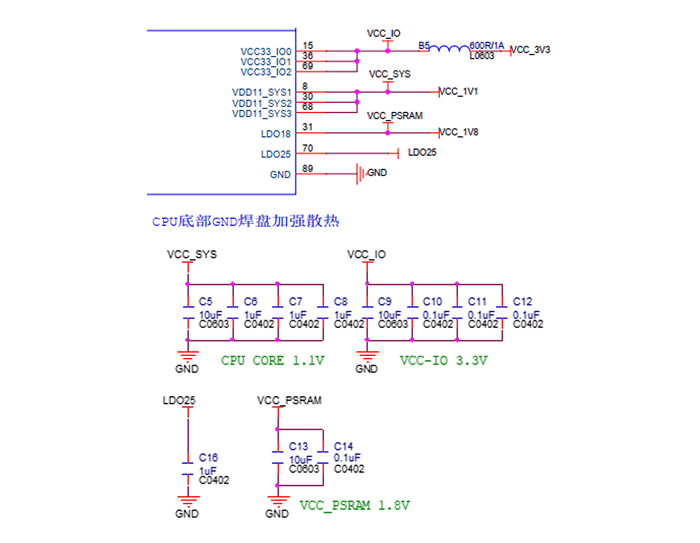

2.2.1. POWER

电源系统

注意

若使用内置LDO18,因转换效率问题,功耗会较外置DCDC增加约60mW,Layout必须做好散热。

若使用内置LDO1x,因转换效率问题,功耗会较外置DCDC显著增加,发热温升高8~10°C,Layout必须做好散热。

图 2.3 Power 电路去耦电容

上下电时序要求

VDD11_SYS、VCC33_IO无上下电时序要求。

复位信号内置约30Kohm上拉电阻和去抖滤波,不使用可直接悬空,若外挂电容建议不超过4.7uF。上电完成后,复位自动释放,并且24MHz晶振起振。

2.2.2. SYS

系统功能脚说明

信号名 |

信号说明 |

应用说明 |

|---|---|---|

UBOOT |

升级模式配置 |

默认使用PA0下拉检测,可在UBOOT或bootloader配置任意IO为

下拉检测或上拉检测进入升级模式,建议预留按键或跳线

|

RESET |

CPU复位脚 |

内部RC上拉,低电平复位,可悬空,建议预留按键或跳线 |

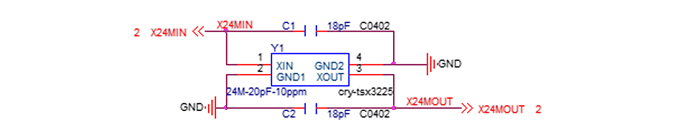

2.2.3. PLL

PLL 需外接24MHz晶振

外部 24MHz 晶振精度要求小于 ±20ppm,匹配电容根据晶体负载电容选择。

PLL_XO 建议串联0R电阻,便于调试振荡幅度。

图 2.4 PLL 24M晶振电路原理图

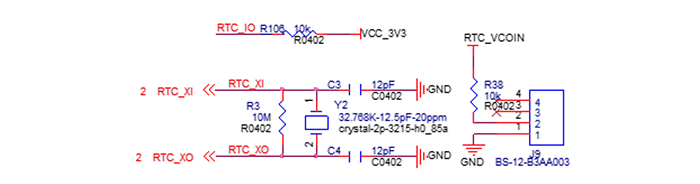

2.2.4. RTC

内置RTC,使用RTC功能需外接32.768kHz晶振

外部32.768kHz晶振精度建议小于 ±10ppm,匹配电容根据晶体负载电容选择。

RTC_XI和RTC_XO之间并接1M以上电阻,可用于频率微调。

RTC_IO为OD输出,使用时需要外挂上拉电阻,上拉电平不超过5V,可用于RTC唤醒或输出32K时钟。

若不考虑掉电保持,RTC_VCOIN可悬空,内部有二极管通路从VCC33_IO取电。

图 2.5 RTC 电路原理图

2.3. 存储

2.3.1. PSRAM

芯片内部默认 Sip 64Mb PSRAM,最高频率 200MHz DDR。

LDO18为芯片内部 1.8V LDO输出,可配置电压为PSRAM供电。

PSRAM 功耗大概1.8V/50mA。

注意

若使用LDO18为PSRAM供电,会存在转换效率和发热问题,需注意GND焊盘加强散热,散热铜皮完整。

若产品方案对发热和功耗敏感,建议PSRAM采用外置DCDC供电。

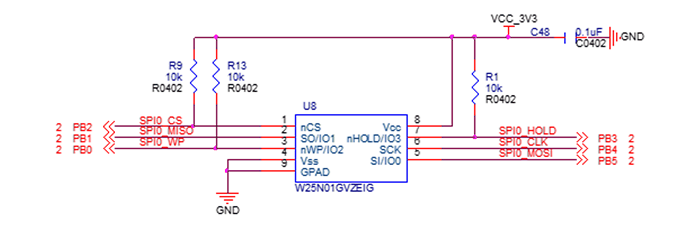

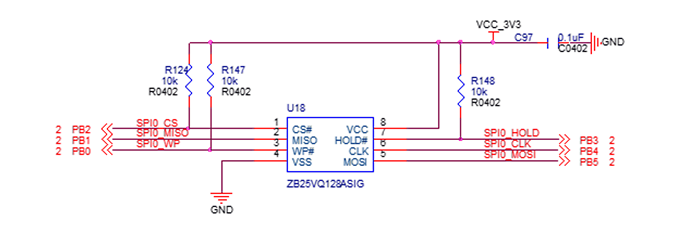

2.3.2. FLASH

SPI0/1/2 为QSPI控制器,最大支持4线数据传输,用于Flash类型设备的快速读写访问。

默认使用 SPI0 为Flash类型设备启动接口。

QSPI 支持 NAND Flash / Nor Flash,支持1/2/4线模式。

IO最大速率 SDR 100MHz,仅支持3.3V IO电压,Flash容量不限制。

注意

SPI_CS、SPI_WP、SPI_HOLD必需保留上拉电阻。

QSPI 信号必需做等长约束,约束不大于20mil,否则跑4线模式容易出现速度跑不高的情况。

图 2.6 SPI0 Nand Flash电路原理图

图 2.7 SPI0 Nor Flash电路原理图

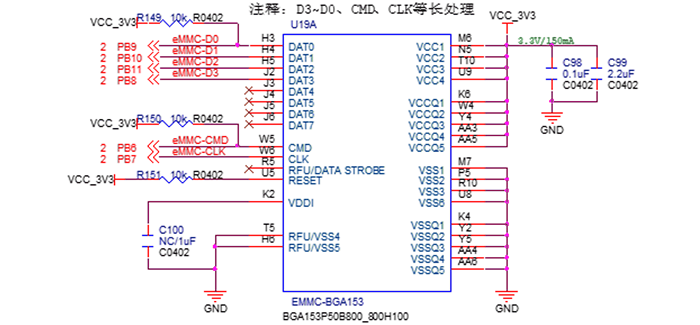

2.3.3. eMMC

使用SDC0接口,1/4线模式,支持eMMC5.0协议,支持SDR25/SDR50/DDR50模式。

IO最大速率 DDR 50MHz,仅支持3.3V IO电压。

D0、CMD和RST信号建议上拉到VCC33_IO。

注意

SDC0_D0~SDC0_D3、SDC0_CLK、SDC0_CMD信号走线做等长约束,约束不大于50mil。

CLK信号不需上拉,最好在靠近主控端串联22欧电阻,若并联容值不超过22pF。

图 2.8 SDC0 eMMC电路原理图

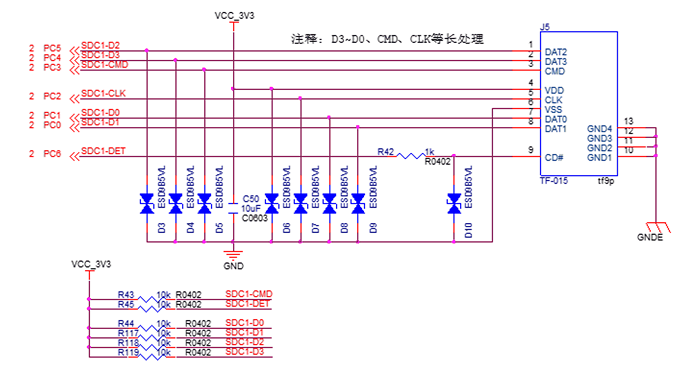

2.3.4. CARD

使用SDC1接口,支持1线、4线模式。

IO最大速率 DDR 50MHz,仅支持3.3V IO电压。

CLK信号不需上拉,最好在靠近主控端串联22欧电阻,若并联容值不超过22pF。

D0、CMD和DET信号建议上拉到VCC33_IO。

SD接口信号线TVS管结电容 < 22pF,否则影响信号传输质量。

建议保留DET信号线上的1k串联电阻,避免在插入SD CARD时产生信号下冲,同时提高GPIO ESD性能。

注意

SDC1_D0~SDC1_D3、SDC1_CLK、SDC1_CMD信号走线做等长约束,约束不大于50mil。

CLK信号不需上拉,最好在靠近主控端串联22欧电阻,若并联容值不超过22pF。

图 2.9 SDC1 CARD电路原理图

2.4. 多媒体

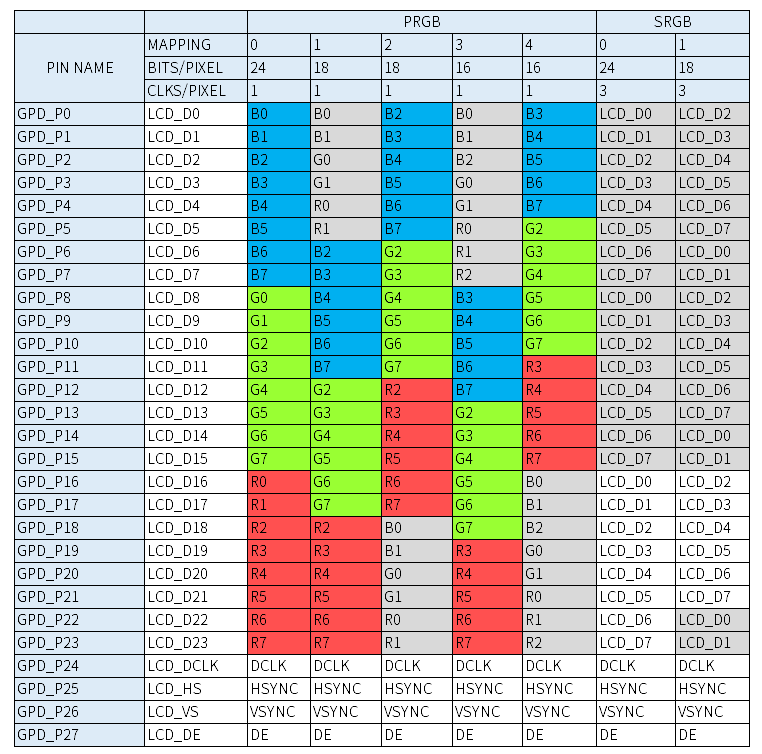

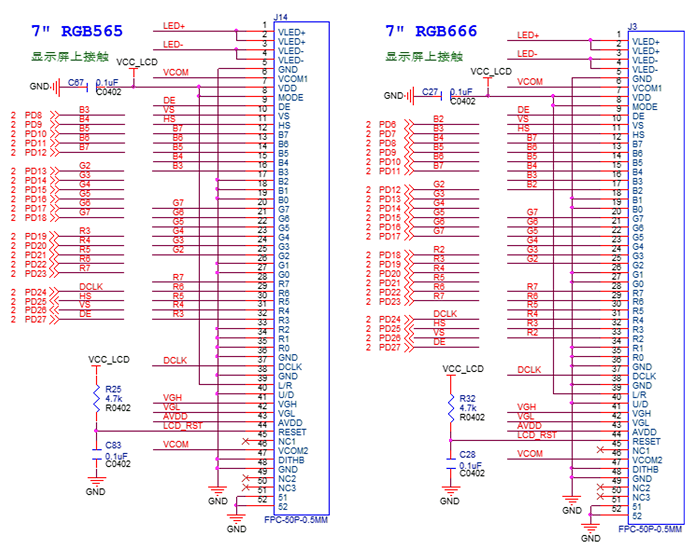

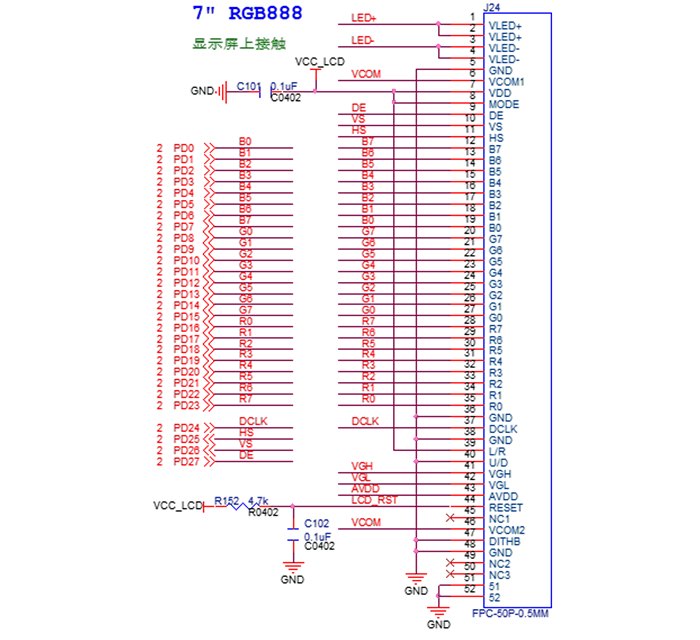

2.4.1. PRGB屏接口

PRGB模式兼容5种MAPPING输出配置,默认为24bits,可配置为18bits、16bits,相应的低位不使用。

配置0:RGB888建议使用,支持R/G/B 整组信号互换,支持组内信号高位到低位排序互换。

配置1:RGB666建议使用,支持R/G/B 整组信号互换。

配置2:RGB666,支持R/G/B 整组信号互换。

配置3:RGB565建议使用,支持R/G/B 整组信号互换。

配置4:RGB565,支持R/G/B 整组信号互换。

注意

只有RGB888支持组内信号高位到低位排序互换,需软件配置data-mirror。

默认配置为RGB,为方便Layout,可将R和B整组互换,需软件配置将data-order修改为BGR。

图 2.10 RGB 不同配置定义

图 2.11 RGB565 / RGB666 电路原理图

图 2.12 RGB888 电路原理图

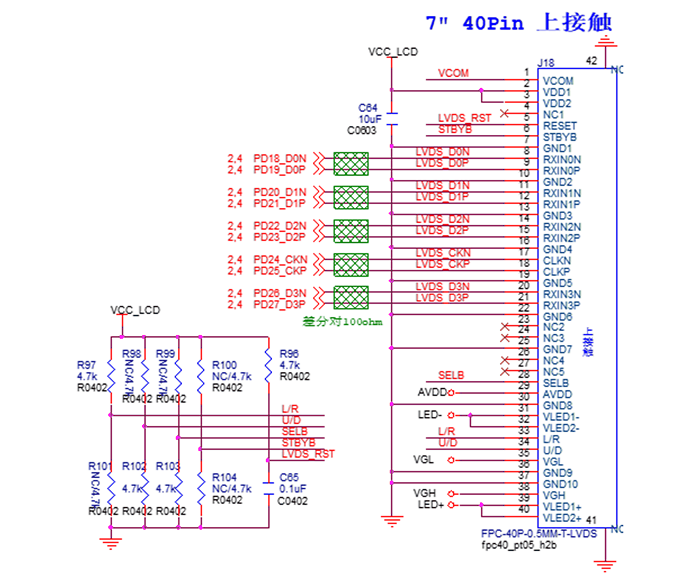

2.4.2. LVDS屏接口

LVDS支持 Single-Link接法。

速率700Mbps。

支持LVDS_D0-LVDS_D3、LVDS_CK五组差分对信号任意互换,比如LVDS_D2与LVDS_CK互换。

支持LVDS信号极性选择模式,即差分对信号正负极性互换。

注意

LVDS信号是高速差分信号,差分对约束不大于10mil,差分对100欧姆阻抗控制,整组信号等长约束不大于10mil。

为方便Layout,支持差分对任意互换,极性反转,软件配置上需注意修改。

图 2.13 LVDS Single-Link 电路原理图

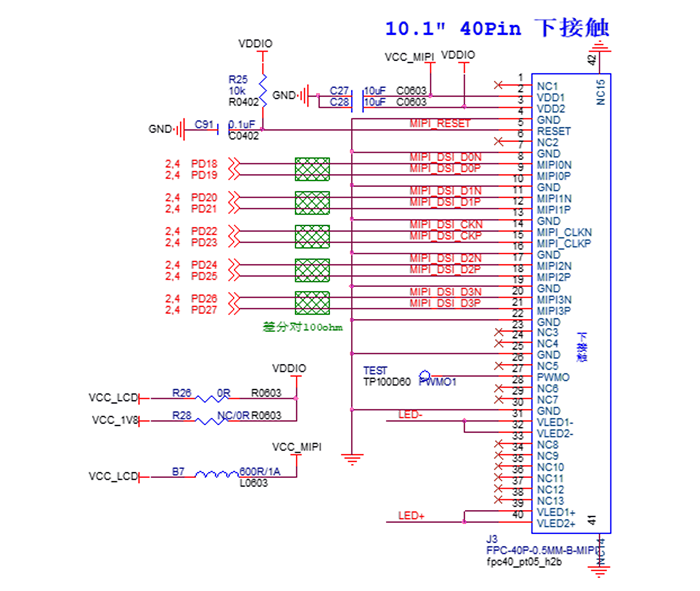

2.4.3. MIPI-DSI屏接口

MIPI DSI是应用于显示的串行接口,实现将DE送过来的并行图像数据高性能转化串行输出。

可配置为1/2/3/4对数据通道。

支持高速模式和低速模式。

每对数据通道都支持高速单向通信。

数据通道0可选支持低速模式下双向通信,即可读取屏的寄存器。

注意

MIPI CLK必须接屏幕的CLK引脚。只支持 D0~D3 差分对信号任意互换。

支持信号极性选择模式,即所有差分对信号支持正负极性反转。

图 2.14 MIPI-DSI 电路原理图

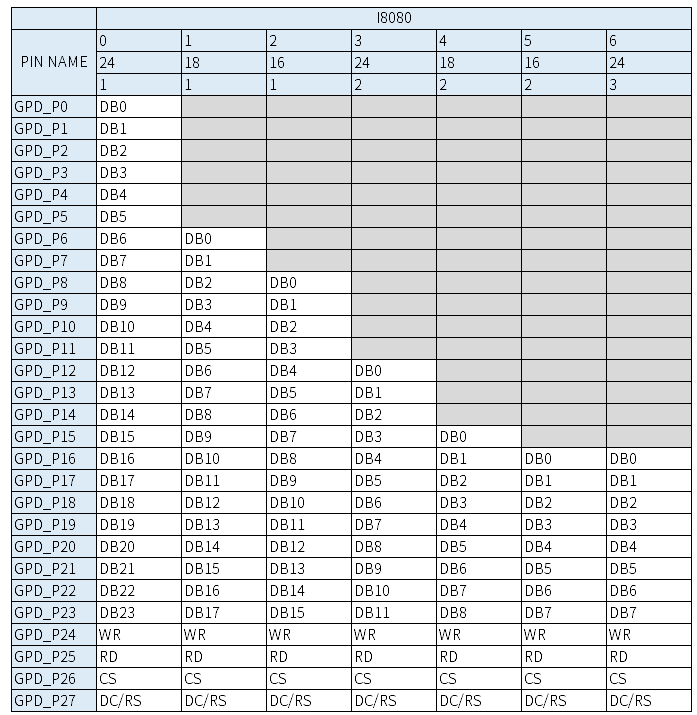

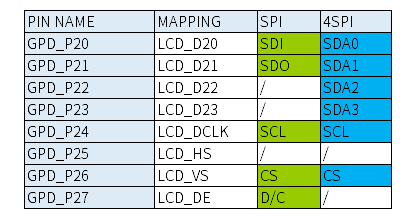

2.4.4. MCU屏接口

MCU屏接口包含常见的I8080、SPI、4线SPI。

图 2.15 I8080 不同配置定义

图 2.16 SPI/4SPI 管脚连接定义

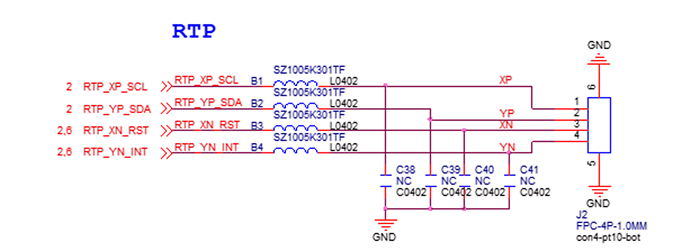

2.4.5. TP

集成 RTP 电阻触摸屏接口,可支持RTP电阻屏触摸。

RTP 仅支持4线,即X+/X-/Y+/Y-。

RTP 支持最多2点触摸。

图 2.17 RTP 电阻屏触摸电路原理图

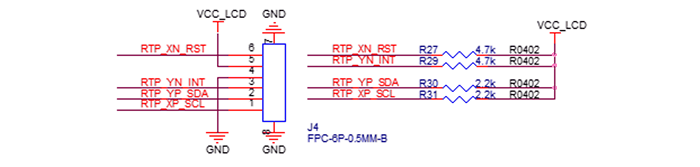

使用I2C和GPIO,可支持CTP电容屏触摸。

图 2.18 CTP 电容屏触摸电路原理图

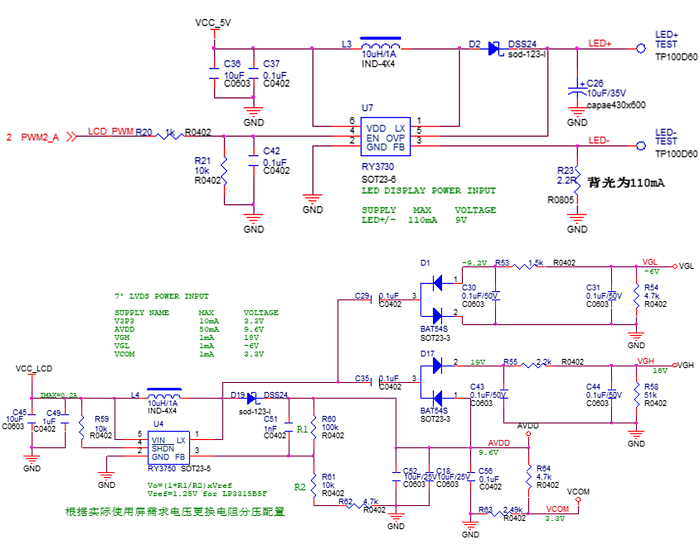

2.4.6. PWM

支持PWM0~PWM3共4组PWM波形发生器

PWMx_A和PWMx_B同属一组PWM,可配置成单独输出或同时输出,但频率相同,占空比可不相同。

PWM通常用于背光控制,频率一般为20kHz~1MHz。

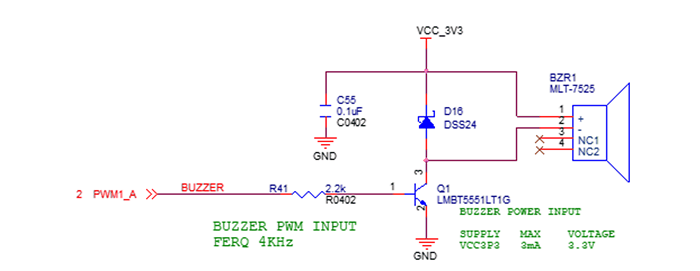

PWM通常用于蜂鸣器,频率一般为3kHz~4kHz。

注意

PWMx_A和PWMx_B可分开独立控制,但频率是相同的,占空比可独立调。

不同频率的应用不能使用同一组PWM,比如蜂鸣器和背光,需分开使用不同通道。

图 2.19 LCD 背光和偏压电路原理图

图 2.20 蜂鸣器电路原理图

2.4.7. DVP

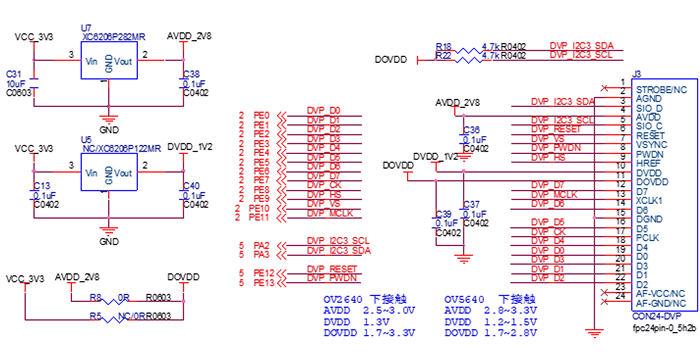

支持 DVP 8位并行接口,最大支持500万像素拍照,最大支持1920x1080@30fps 录像,支持YUV422、BT.656以及RAW格式。

图 2.21 DVP CAMERA 原理图

2.4.8. AUDIO

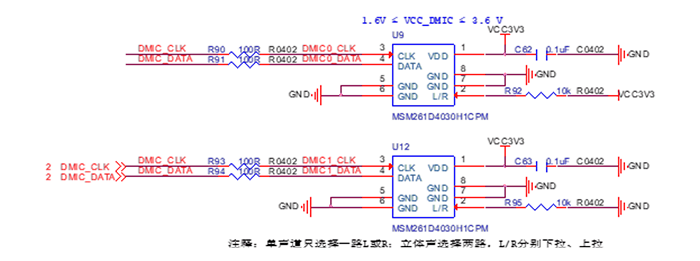

DMIC,支持数字立体声音频输入。

图 2.22 DMIC 电路原理图

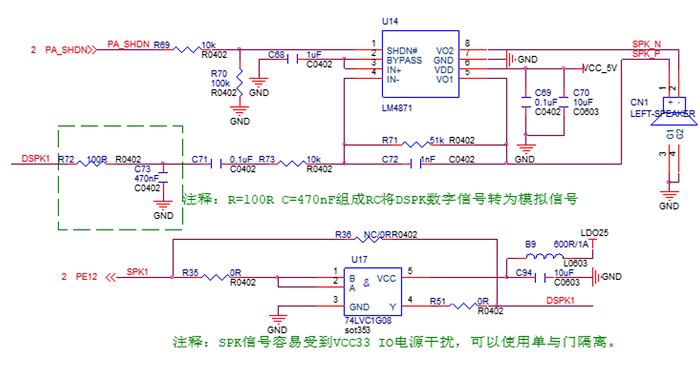

Speaker

支持2路单端输出(双喇叭,左右声道输出)。

支持1路差分输出(单喇叭,单声道输出)。

支持DSPK0和DSPK1内部混音后,再通过任意单一通路输出。

注意

DSPK是数字信号,从CPU出来必需接RC(R=100R,C=470nF)转换成模拟信号才能给到音频功放。

DSPK信号容易受到VCC33_IO电源干扰,需使用干净电源比如LDO25给单与门供电进行信号隔离。

图 2.23 Speaker 单端输出电路原理图

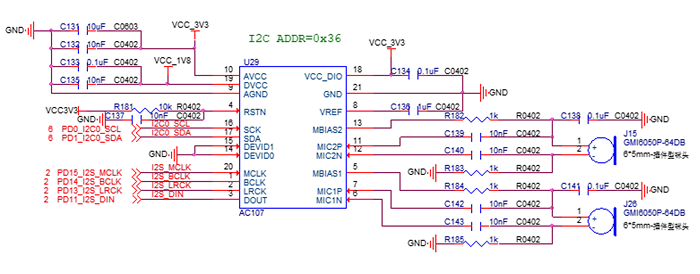

I2S

I2S接口为数字音频接口,用于连接外部音频设备,实现音频数据的传输。

图 2.24 I2S 扩展麦克风电路原理图

2.5. 通用接口

2.5.1. ETHERNET

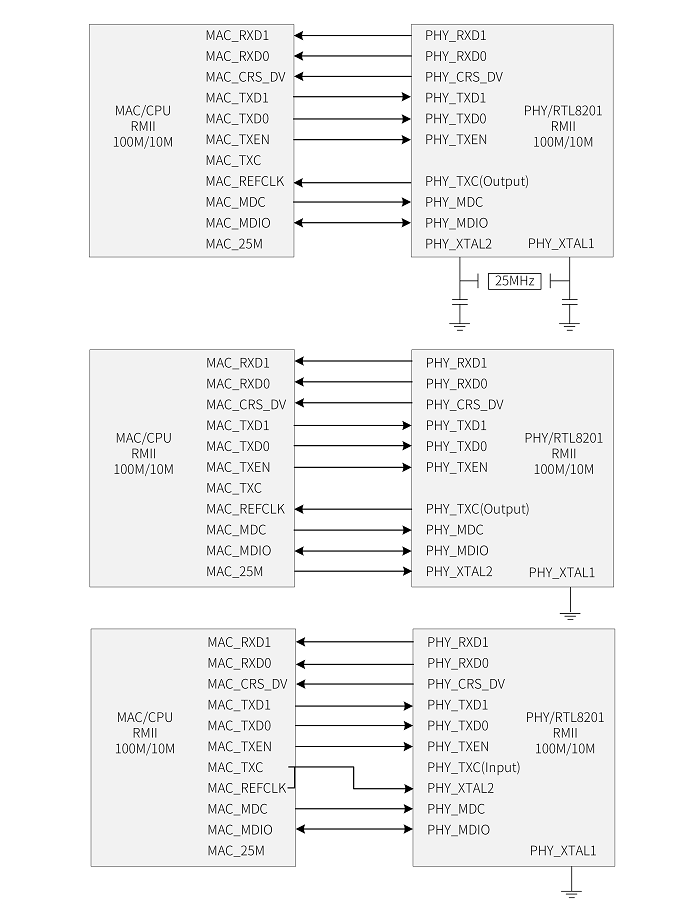

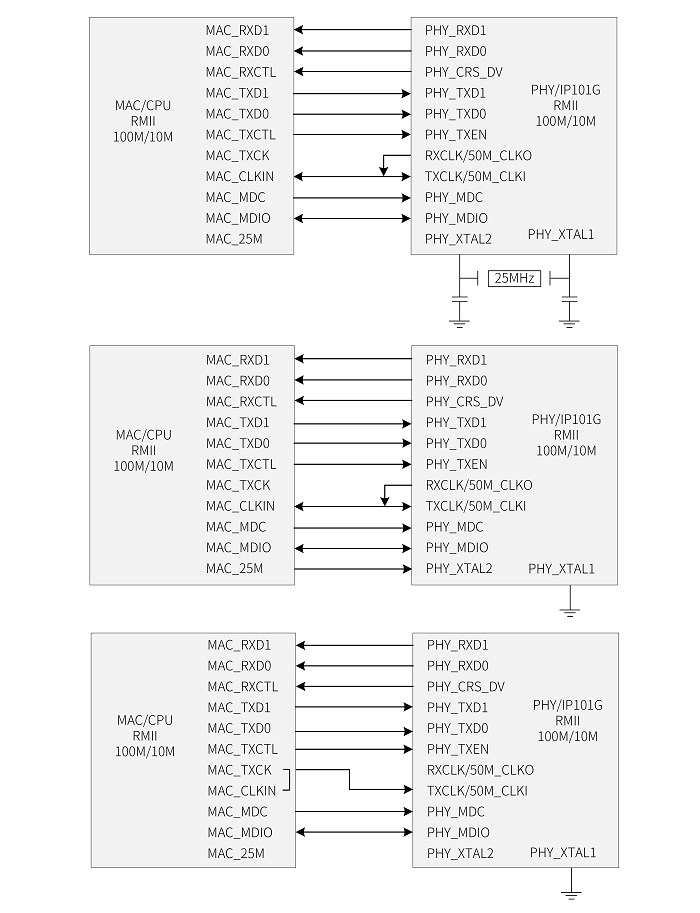

RMII 内部参考时钟(外部PHY_TXC为Input情况)

MAC_REFCLK 时钟不使能,内部选通PLL_EMAC_50M作为RMII 50MHz参考时钟源

MAC_TXC 输出时钟,提供给外部PHY使用

MAC_TXC 输出时钟接外部PHY_TXC Input

RMII 外部参考时钟(外部PHY_TXC为Output情况或晶振提供50MHz)

MAC_REFCLK 时钟使能,并且选通作为RMII 50MHz参考时钟源

MAC_TXC不使能,无需提供外部PHY时钟信号

MAC_REFCLK 输入时钟接外部PHY_TXC Output

注意

使用PHY_TXC提供参考时钟时,MAC_TXC可不使用,对应管脚可用于其他功能。

使用MAC_TXC提供参考时钟时,MAC_REFCLK可不使用,对应管脚可用于其他功能。

MAC端信号 |

RMII接口 |

类型 |

描述 |

PHY端信号 |

|---|---|---|---|---|

MAC_RXD1 |

RMII_RXD1 |

I |

数据接收信号线1 |

PHY_RXD1 |

MAC_RXD0 |

RMII_RXD0 |

I |

数据接收信号线0 |

PHY_RXD0 |

MAC_CRS_DV |

RMII_CRS_DV |

I |

数据接收有效 |

PHY_CRS_DV |

MAC_REFCLK |

RMII_REF_CLK |

I |

参考时钟 |

PHY_TXC(Output) |

MAC_TXD1 |

RMII_TXD1 |

O |

数据发送信号线1 |

PHY_TXD1 |

MAC_TXD0 |

RMII_TXD0 |

O |

数据发送信号线0 |

PHY_TXD0 |

MAC_TXC |

RMII_TXC |

O |

数据发送时钟 |

PHY_TXC(Input) |

MAC_TXEN |

RMII_TXEN |

O |

数据发送使能 |

PHY_TXEN |

MAC_MDC |

RMII_MDC |

I/O |

串行管理接口时钟 |

PHY_MDC |

MAC_MDIO |

RMII_MDIO |

I/O |

串行管理接口数据 |

PHY_MDIO |

CLK_OUT |

CLK_OUT |

O |

25MHz时钟 |

PHY_XTAL2 |

图 2.25 RTL8201 三种接法框图

图 2.26 IP101G 三种接法框图

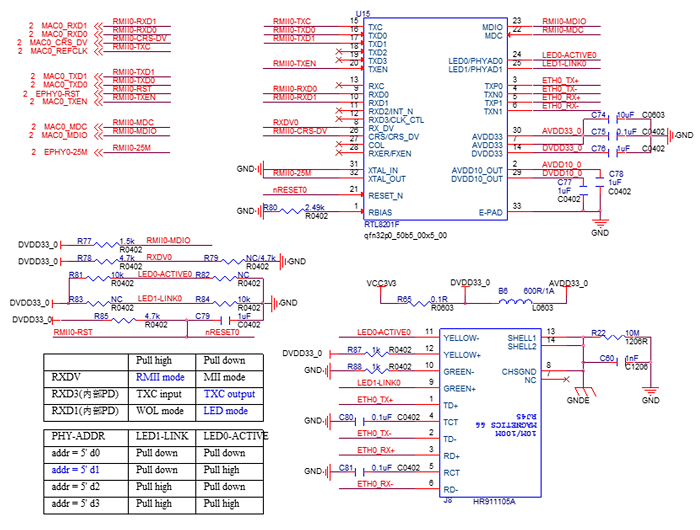

图 2.27 RTL8201 RMII 电路原理图

防护设计

可用 TVS 阵列来保护 TXP、TXN、RXP 和 RXN 信号。

可用铁氧体磁珠和隔离变压器来分别隔离电源和信号线上的高频噪声。

可用 RC 或铁氧体磁珠隔离网络接口屏蔽层和信号地,以提高 ESD 性能。

2.5.2. SPI

SPI0/1/2/3为标准SPI控制器,用于存储设备或其他SPI接口设备的访问。

均支持Master和Slave。

SPI0/1/2 支持QSPI 1/2/4线模式。

SPI3 支持SPI 1线模式。

2.5.3. UART

UART兼容工业16550标准,支持常用波特率,最大波特率支持10Mbps。

支持UART 2线(TX、RX),通常应用于TTL、RS485、RS232、DEBUG打印。

支持UART 3线(TX、RX、RTS),通常应用于RS485、某些模块比如RTL8723DS其蓝牙只需UART 3线。

支持UART 4线自动流控(TX、RX、RTS、CTS),通常应用于RS232、蓝牙通信。

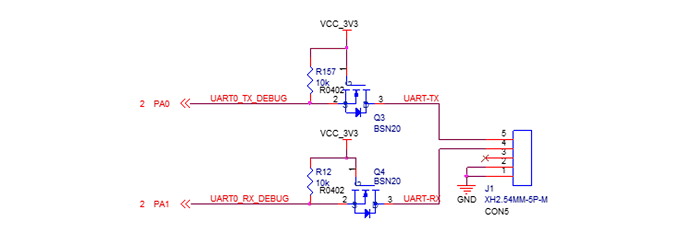

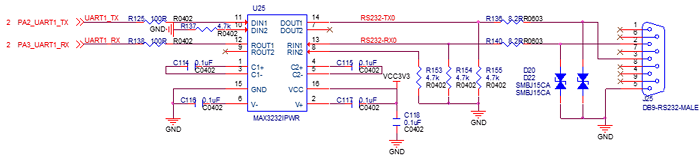

图 2.28 调试串口电路原理图

图 2.29 RS232串口电路原理图

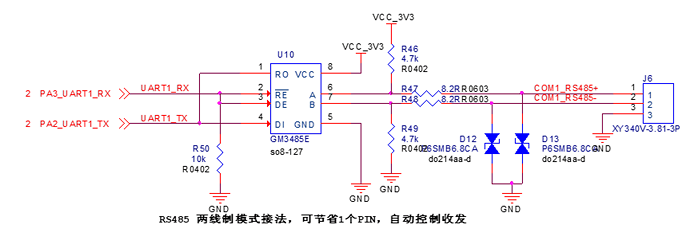

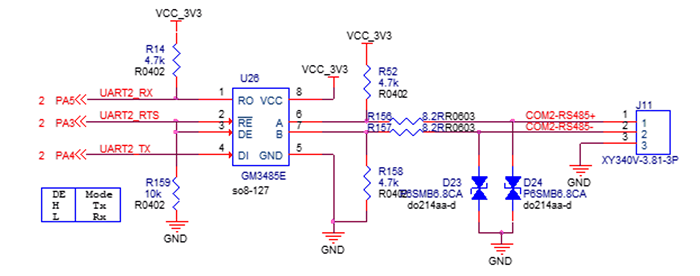

RS485支持硬件自动控制收发方向,也支持软件控制收发方向

在IO资源紧张时,建议采用两线接法,通过UART_TX管脚进行半双工收发,UART_RX管脚进行自动方向控制。

需要做光耦隔离时,可采用常规三线接法,UART_RTS管脚进行自动方向控制。

注意

使用两线接法时,TX管脚既当发送又当接收;RX管脚用于自动控制收发方向。

使用三线接法时,建议使用UART_RTS接485-DIR,方便使用硬件自动控制收发功能。

图 2.30 RS485 两线接法电路原理图

图 2.31 RS485 三线接法电路原理图

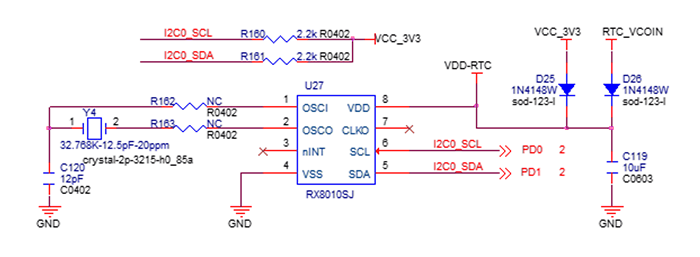

2.5.4. I2C

I2C速率最大支持400kbps,支持master 和 slave 模式。

图 2.32 I2C 外接RTC电路原理图

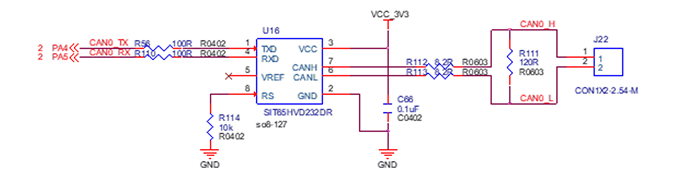

2.5.5. CAN

支持CAN0控制器

支持CAN2.0A和CAN2.0B协议,可编程通信速率最高1Mbps。

外围电路需接收发器,才能组成CAN总线网络。

图 2.33 CAN 电路原理图

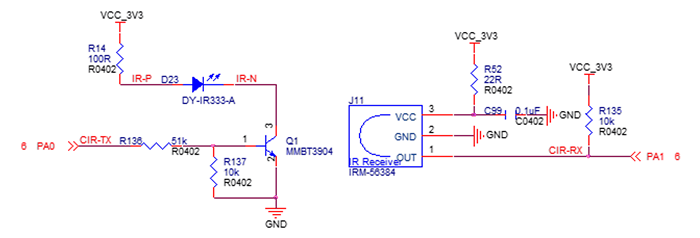

2.5.6. CIR

支持市面常见红外协议,如NEC、RC5、RC6、RC-MM、Sony、Sanyo、JVC等。

图 2.34 CIR 红外收发电路原理图

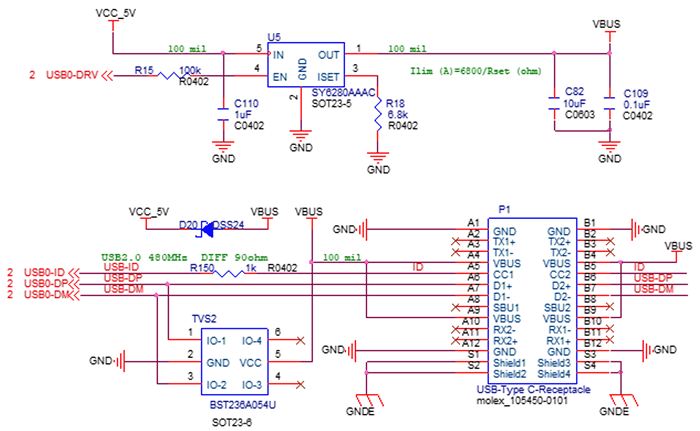

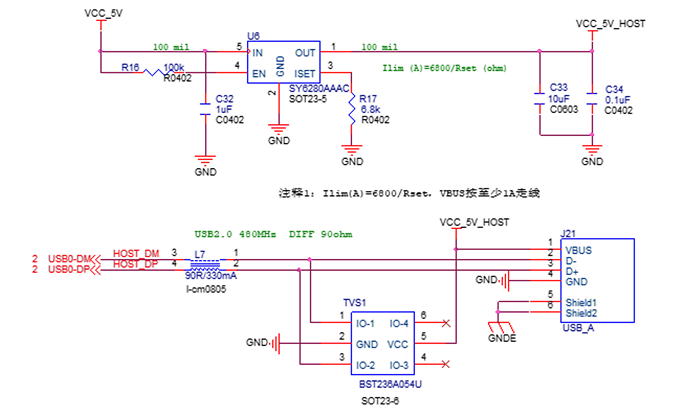

2.5.7. USB

USB 可支持 Device 或 Host,可用于烧录程序或接外部设备。

USB 插座ID脚用于检测外部设备类型。当ID脚为低则工作在Host模式,当ID脚为高则工作在Device模式。

USB ID信号建议串联电阻,避免插入设备时产生信号下冲,同时提升GPIO口ESD性能。

USB DP、DM信号为高速差分信号线,差分走线阻抗控制90 ohm,TVS管寄生电容建议小于5pF。

USB 插座VBUS建议不要与板卡5V直连,中间串入二极管,避免VCC_5V和VBUS同时供电时影响。

USB 电源建议增加限流开关,避免插入HOST设备瞬态电流过大。

注意

USB_ID可连接到任意GPIO,可用于检测设备类型切换Device 或 Host。

可通过软件指令动态切换 Device 或 Host。

图 2.35 USB OTG电路原理图

图 2.36 USB HOST电路原理图

防护设计

可用 TVS 阵列来保护 VBUS、D+、D-和 ID 信号。

可在 USB 差分信号上串联共模扼流圈,改善 EMI 性能。

可在 VBUS、GND 上串联铁氧体磁珠,隔离高频噪声。

可用 RC 电路或铁氧体磁珠隔离 USB 外壳和信号地,提高 ESD 性能。

2.5.8. SDIO

SDC0/SDC1 可用于用于访问SDIO接口的设备,比如eMMC、CARD、WIFI模组。

SDIO 接口只支持 3.3V IO 电平,接口顺序关系需注意。

SDIO 接口按等长约束走线,CLOCK 尽量包地处理。

天线端增加 TVS 管,防止 ESD 静电打坏模块。

所有电源滤波电容尽量靠近芯片电源输入脚放置。

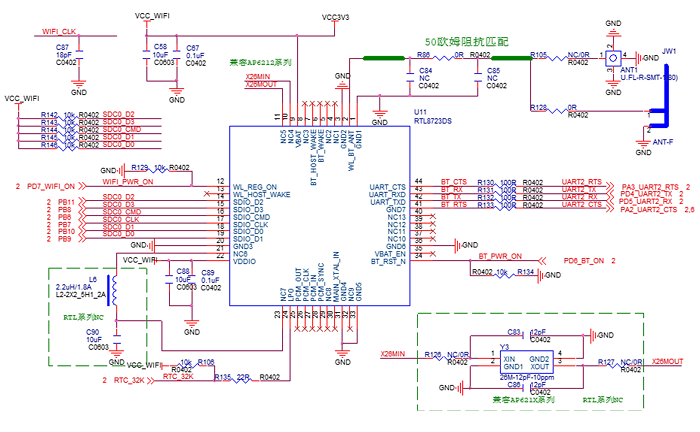

图 2.37 SDC0 WIFI+BT 电路原理图

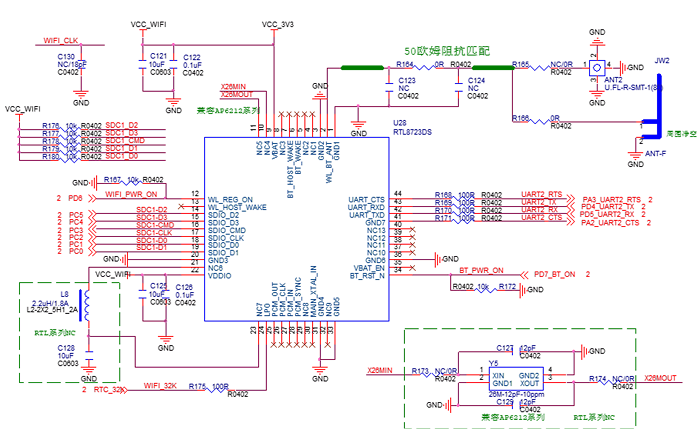

图 2.38 SDC1 WIFI+BT 电路原理图