6.2.9. 常见问题

6.2.9.1. PRGB接口屏

6.2.9.1.1. 现象一:黑屏

检查背光是否已亮

排除1后确定屏规格书是SYNC模式还是DE模式,检查硬件电路相关控制信号是否按照屏规格书要求完成上下拉

排除1、2后,测量pixelclk是否符合屏规格要求,pixelclk计算公式如下:

pixelclk = (hactive + hback-porch + hfront-porch + hsync-len)

* (vactive + vback-porch + vfront-porch + vsync-len) * 帧率

时钟频率 = 有效+消隐的总时间 * 帧率

6.2.9.1.2. 现象二:花屏

调整pixelclk频率

调整pixelclk相位

调整消隐区参数,主要是行方向消隐区

6.2.9.1.3. 现象三:起始位置错误

调整pixelclk频率

调整pixelclk相位

调整消隐区参数,主要是行方向消隐区

6.2.9.1.4. 现象四:闪烁

增大pixelclk频率,提高帧率

6.2.9.2. LVDS接口屏

6.2.9.2.1. 现象一:黑屏

检查背光是否已亮

排除1后,检查LVDS通道是否连接正确,检查硬件电路相关控制信号是否按照屏规格书要求完成上下拉,检查屏规格书是VESA模式还是JEIDA模式

排除1、2后,测量pixelclk是否符合屏规格要求,LVDS接口中有一对时钟差分信号CK,若为单通道,则实测pixelclk=7ck;若为双通道,则实测pixelclk=3.5ck;

6.2.9.2.2. 现象二:花屏

调整pixelclk频率

调整消隐区参数,主要是行方向消隐区

6.2.9.2.3. 现象三:起始位置错误

调整pixelclk频率

调整消隐区参数,主要是行方向消隐区

6.2.9.2.4. 现象四:闪烁

增大pixelclk频率,提高帧率

6.2.9.3. DSI接口屏

6.2.9.3.1. 现象一:黑屏

检查背光是否已亮

排除1后,检查硬件电路相关控制信号是否按照屏规格书要求完成上下拉;检查与屏的连接是否成功,通常使用读屏驱动ID检查;检查初始化流程是否正确,检查屏规格书是Commad模式还是Video模式

排除1、2后,测量pixelclk是否符合屏规格要求。

6.2.9.3.2. 现象二:花屏

检查屏数据格式,检查数据lane数量

调整pixelclk频率

调整消隐区参数,主要是行方向消隐区

6.2.9.3.3. 现象三:起始位置错误

调整pixelclk频率

调整消隐区参数,主要是行方向消隐区

6.2.9.3.4. 现象四:闪烁

增大pixelclk频率,提高帧率

6.2.9.4. DBI接口屏

6.2.9.4.1. PCLK计算

像素时钟计算公式:Pclk = ( active_h+hbp+hfp+hsync)* ( active_v+vbp+vfp+vsync)*60

u32 active_h = 360;

u32 active_v = 480;

u32 hbp = 10;

u32 hfp = 10;

u32 vbp = 20;

u32 vfp = 8;

u32 hsync = 20;

u32 vsync = 10;

以360*480分辨率60帧为例,Pclk = (360+10+10+20)*(480+20+8+10)*60 = 12.43MHz ,取整13MHz 像素时钟快速估算公式: Pclk=360*480*60/0.8 ≈ 13MHz,0.8为考虑消隐区参数后的估算系数。

QSPI:做显示接口最大速度50M

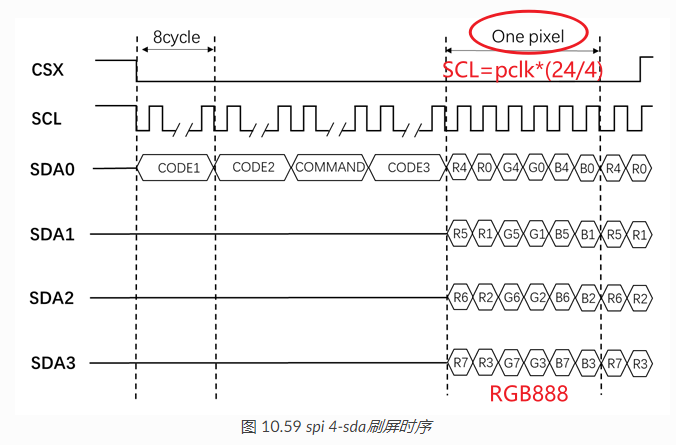

DE每个Pclk并行输出RGB888 24bit给到显示接口,QSPI 4根数据线,需要6个SCL才能传输完一个像素,理论上SCL=Pclk*6=78MHz,频率超出接口最大速度有风险;

DE每个Pclk并行输出RGB565 16bit给到显示接口,QSPI 4根数据线,需要4个SCL才能传输完一个像素,理论上SCL=Pclk*4=52MHz,频率接近接口最大速度可接受;

SPI:做显示接口最大速度100M

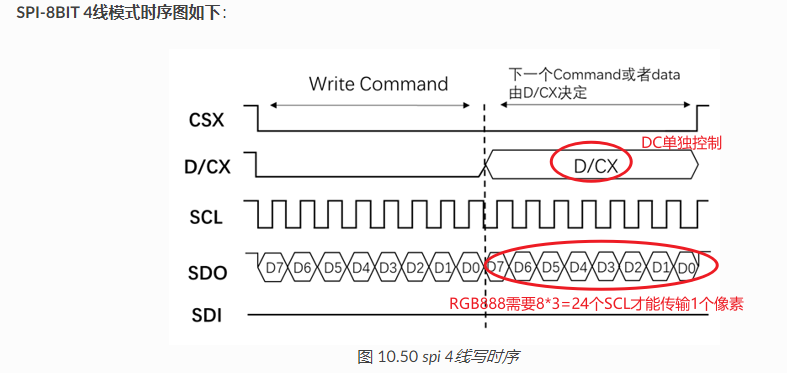

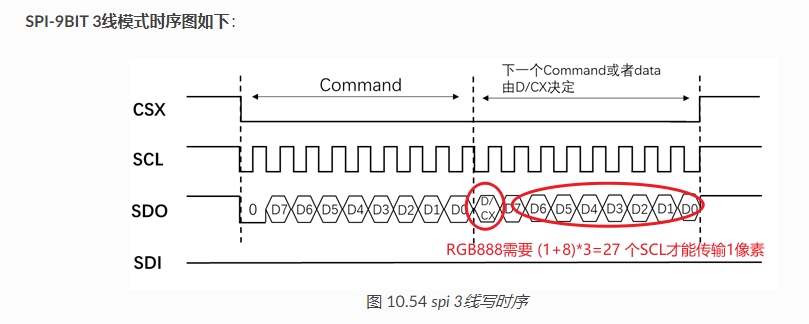

DE每个Pclk并行输出RGB888 24bit给到显示接口,SPI-8bit 4线模式,需要24个SCL才能传输完一个像素,理论上SCL=Pclk*24=312M,显然超出接口最大速度范围,此时只能换QSPI接口、降帧率或支持的分辨率变小;

DE每个Pclk并行输出RGB565 16bit给到显示接口,SPI-8bit 4线模式,需要16个SCL才能传输完一个像素,那理论上SCL=Pclk*16=208M,显然超出接口最大速度范围,此时只能换QSPI接口、降帧率或支持的分辨率变小;

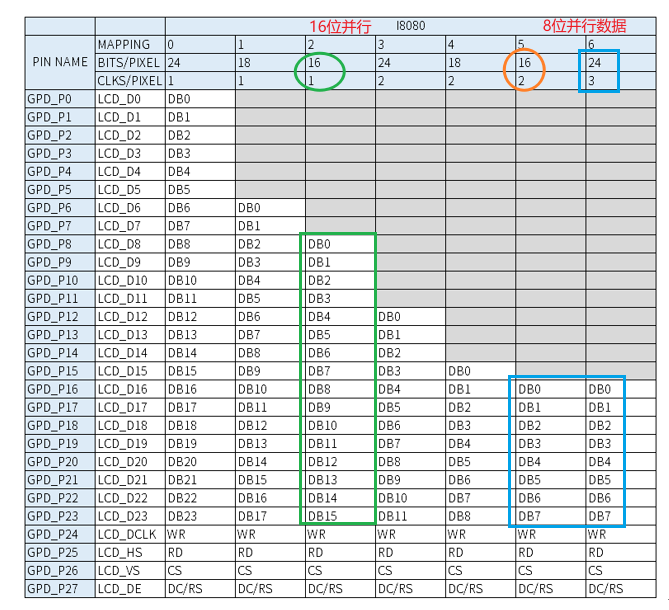

I8080:做显示接口最大速度50M

DE每个Pclk并行输出RGB888 24bit给到显示接口,I8080接口8位并行数据线,需要3个SCL才能传输完一个像素,理论上WR/SCL=Pclk*3=39M;

DE每个Pclk并行输出RGB888 24bit给到显示接口,I8080接口16位并行数据线,需要2个SCL才能传输完一个像素,理论上WR/SCL=Pclk*2=26M;

DE每个Pclk并行输出RGB565 16bit给到显示接口,I8080接口8位并行数据线,需要2个SCL才能传输完一个像素,理论上WR/SCL=Pclk*2=26M;

DE每个Pclk并行输出RGB565 16bit给到显示接口,I8080接口16位并行数据线,需要1个SCL才能传输完一个像素,理论上WR/SCL=Pclk*1=13M;

PRGB

以4.3寸480*272分辨率60帧为例,Pclk=480*272*60/0.8≈9.8MHz,通常取9MHz

以4.3寸800*480分辨率60帧为例,Pclk=800*480*60/0.8≈28.8MHz,通常取27MHz

以7寸1024*600分辨率60帧为例,Pclk=1024*600*60/0.8≈46MHz-