8.1.2. 参数配置

8.1.2.1. 内核配置

使能 SPI_ENC 相关的内核驱动,可在通过下列命令进行配置(参考:快速入门 - 编译概述 - Kernel配置):

make menuconfig

在内核的配置界面中,进行下列的选择:

Cryptographic API --->

[*] Hardware crypto devices --->

[*] Support for zx cryptographic accelerator

<*> ZX's SPI Bus on-the-fly encryption driver

进行如上的配置之后,内核 SPI_ENC 驱动使能,SPI NOR / SPI NAND 驱动在数据访问时, 自动进行数据加解密。

8.1.2.2. DTS 配置

芯片级的 DTS:

spienc: spienc@18100000 {

compatible = "zx,aic-spienc-v1.0";

reg = <0x18100000 0x1000>;

interrupts-extended = <&plic0 41 IRQ_TYPE_LEVEL_HIGH>;

clocks = <&cmu CLK_SPIENC>;

resets = <&rst RESET_SPIENC>;

aic,spienc-tweak = <0>;

};

其中板级的配置 board.dts 中需要使能该模块:

&spienc {

aic,spienc-tweak = <0>;

status = "okay";

};

board-u-boot.dtsi 需要设置 u-boot,dm-pre-reloc ,只有设置了该标记,SPL 中才可以使用 SPI_ENC:

&spienc {

u-boot,dm-pre-reloc;

};

DTS 中的 aic,spienc-tweak 可以影响 COUNTER 的生成,进而改变加密的结果。

如果需要让在不同的产品对相同的数据有不同的加密结果,则可以在 DTS 中调整该值。

并且需要配置具体的 SPI NAND / SPI NOR 设备是否使能加密:

aic,encrypt

aic,spi-id

例如: board.dts

&spi0 {

pinctrl-names = "default";

pinctrl-0 = <&spi0_pins_a>;

status = "okay";

spi-flash@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "spi-nand";

spi-max-frequency = <24000000>;

spi-tx-bus-width = <1>;

spi-rx-bus-width = <1>;

reg = <0>;

aic,encrypt; // 标记该存储设备使能 SPI_ENC

aic,spi-id = <0>; // 设置当前存储设备所挂载的 SPI 控制器 ID

status = "okay";

};

};

&spi1 {

pinctrl-names = "default";

pinctrl-0 = <&spi1_pins_a>;

status = "okay";

spi-flash@0 {

#address-cells = <1>;

#size-cells = <1>;

compatible = "jedec,spi-nor";

spi-max-frequency = <24000000>;

spi-tx-bus-width = <1>;

spi-rx-bus-width = <1>;

reg = <0>;

aic,encrypt; // 标记该存储设备使能 SPI_ENC

aic,spi-id = <1>; // 设置当前存储设备所挂载的 SPI 控制器 ID

status = "okay";

};

};

8.1.2.3. 密钥配置

SPI_ENC 模块使用 AES-128-CTR 算法对 SPI 总线数据进行加解密,该算法在计算时的密钥有两部分

128 bit AES 密钥(KEY)

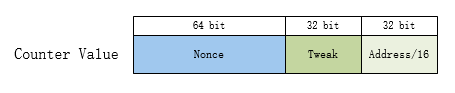

128 bit 数据块的 COUNTER 值

其中 KEY 直接使用 eFuse 中的 SPI_ENC_KEY ,COUNTER 值则由几部分共同产生

eFuse 中的

SPI_ENC_NONCEDTS 中配置的

aic,spienc-tweak访问数据所在的地址

address

图 8.8 COUNTER 值的生成

因此在使能 SPI_ENC 时,需要设置以下的 eFuse 信息:

eFuse 区域 |

大小(BIT) |

说明 |

|---|---|---|

SPI_ENC_KEY |

128 |

AES 密钥,烧录后应设置不可读写 |

SPI_ENC_NONCE |

64 |

用于生成 COUTNER 的随机数,烧录后应设置不可读写 |

SPI_ENC_ENABLE BIT |

1 |

使能 BROM 的 SPI_ENC 功能,才可正确启动 |

具体 eFuse 区域的地址,请参考芯片的数据手册。