8.1.2. 功能描述

8.1.2.1. 总线接口模块

AHB从机接口

通过AHB接口访问Host控制器,控制器内部使用AHB从机接口连接AHB主机。

当使用AHB总线访问寄存器时,每笔寄存器访问都需要等待一个时钟周期。

当使用AHB访问数据FIFO时:

对于单笔传输方式,每笔传输需要等待一个时钟周期;

对于突发传输方式,访问第一个数据需要等待一个时钟周期,接下来的访问则不用等待。

在访问FIFO区域的部分数据时,当被访问的数据地址与FIFO地址对齐时,FIFO数据才会发生pop或push操作。 例如,如果FIFO数据位宽为32位,

当访问32位数据时,FIFO直接发生pop或push操作;

当访问16位数据时,地址线[0]=1时,发生pop或push操作;

当访问8位数据时,地址线[1:0]=11b时,发生pop或push操作。

对于部分写操作,数据先存储在临时寄存器内,直到FIFO数据地址与FIFO地址对齐时,才真正写入FIFO。 因此,建议对FIFO进行全位宽访问。如果需要进行部分位宽访问,一定要优先访问低字节位。

寄存器单元

寄存器单元是总线接口模块的一部分,它提供了寄存器的读写访问功能。控制器最大支持的总线位宽为64bits, 本芯片寄存器设计为32bits位宽。除了TCBC和TFBC寄存器以外,其他的寄存器都可以选择访问8/16/32位宽, 这由Host总线接口位宽和byte_enable控制信号共同决定。

所有的寄存器都属于HIF时钟域。当一个命令发送到Card,应设置CMD寄存器的start_bit位, 所有需要CIF操作的相关寄存器发送到CIF模块。此时,从HIF到CIF的寄存器不能被写入。 再次写入这些寄存器之前,软件应该等待硬件清零start bit位。寄存器单元具有硬件锁功能,防止非法写入寄存器。

备注

一旦start_bit置位,还没有硬件清零时,以下寄存器不能再次写入:

CMD

CMDARG

CLK_CTRL

TMOUT

BUS_WIDTH

中断控制单元

中断控制单元产生中断信号,该信号由控制器的初始中断状态寄存器,中断使能寄存器,以及全局中断使能寄存器位决定。 一旦某个中断条件被检测到,初始中断状态寄存器对应的中断位会置1。初始中断状态位保持,直到通过软件写1清零。

FIFO控制单元

FIFO控制器连接内部FIFO到Host接口,以及卡控制器单元。FIFO深度为128,FIFO位宽为32位。由于读和写传输不会同时发生, 可以使用一个共享FIFO用于读写传输,以节省芯片面积。因为允许使用部分总线位宽访问FIFO, 此时会使用临时寄存器先存储低字节数据,直到高字节数据到来时才真正访问FIFO。

卡检测单元

卡检测单元用于检测SD卡插入和拔出时信号电平变化。通过一个去抖计时器来延迟检测时间,避免由于机械插拔造成的信号抖动, 并产生一个中断信号发送给Host。用户可以通过编程Debounce寄存器设置去抖时间。上电后,控制器读取卡检测端口的状态值并将其存储到内存里, 每次检测的状态值都与之前的状态值进行异或并更新到Card_detect_n寄存器。

卡检测信号连接到卡座上,需要进行外部上拉,当没有卡插入时检测到高电平,Card_detect_n寄存器置1;当检测到卡插入,该检测脚通过卡座连接到地, 检测到低电平,Card_detect_n寄存器为0。

备注

只有SDMC1控制器支持硬件卡检测模块,其他控制器可以通过GPIO进行卡检测。

8.1.2.2. 内部DMA控制器

内部DMA控制器(IDMAC)由控制寄存器,状态寄存器,和单向发送/接收引擎组成。控制器使用一个有效的描述符 将数据从源地址搬移到目标地址,使CPU干预最小化。IDMAC和Host驱动之间的通信使用单个数据结构, IDMAC从Card接收数据存储到Host内部的数据缓存,从数据缓存读取数据发送到FIFO。存储在Host内部的描述符, 作为指针指向这些数据缓存。

在Host内部物理存储空间包含一个数据缓存区,它由完整数据或部分数据组成。该缓存区仅包含数据, 缓存的状态包含在描述符中。数据链是指数据跨多个数据缓存。然而,单个描述符不会跨多个数据。

单个描述符用于接收和发送数据。链表的基址写入描述符链表基址寄存器(IDMASADDR)。描述符链表向前连接, 最后一个描述符可以指回到第一个描述符,形成一个环状结构。描述符链表属于Host物理内存地址空间。 每个描述符可以指向两个数据缓存中最大的一个。

通过配置HCTRL1寄存器的bit25,使能或禁用IDMAC。如果IDMAC被禁用,可以通过AHB总线的Slave接口访问数据。 如果IDMAC使能,则不能通过Slave接口访问FIFO。

描述符

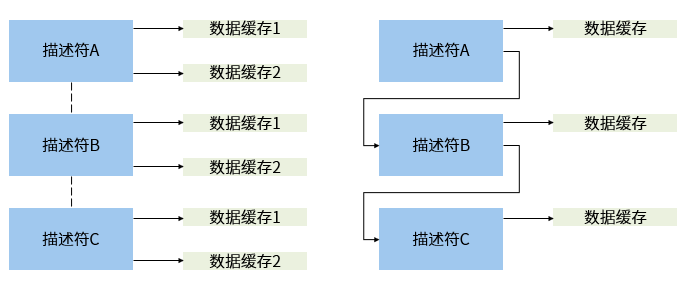

IDMAC使用两种描述符结构:

双缓存结构:两个描述符的间隔,通过PBUSCFG寄存器的DSL位域进行编程。

链式结构:每个描述符指向唯一的缓存和下一个描述符地址。

两种描述符结构见下图:

描述符地址必须按照32位数据位宽对齐,每个描述符包含16字节的控制和状态信息,由4个DES寄存器组成,每个DES都存储32位数据。

DES0用于配置控制信息,说明如下:

位域 |

位域名称 |

说明 |

|---|---|---|

31 |

OWN |

该位置1,表示描述符由IDMA控制。当该位复位,表示描述符由Host控制。

当数据传输完成时,IDMA控制器对该位清零。

|

30 |

CES(Card Error Summary) |

该错误位表示发送到Card和来自Card的状态,该位也存在于OINTST

寄存器,与以下位域为逻辑或的关系:

BE:结束位错误

TO:响应超时

CRC:响应数据CRC错误

RTO:数据读超时

CRC:数据接收CRC错误

RE:响应错误

|

29:6 |

RESET |

/

|

5 |

ER(End of Ring) |

该位置1,表示描述符链表到达最后一个描述符。

IDMA控制器返回链表的基址,创建一个描述符环。

仅在双缓存描述符结构时有效。

|

4 |

CH(Second Address Chained) |

该位置1,表示描述符的第二个地址是下一个描述符的地址,不是第二个缓存

的地址。该位置1时,DES1[25:13]应该清零。

|

3 |

FS(Fist Descriptor) |

该位置1,表示描述符包含第一个缓存的数据。如果第一个缓存的容量为0,

下一个描述符包含起始数据。

|

2 |

LD(Last Descriptor) |

该位与一次DMA传输的最后一个block有关。

该位置1,表示缓存指向该描述符的最后一个缓存数据。该描述符结束后,

剩余的字节数为0。即描述符完成后且该位置1时,剩余字节数为0。

|

1 |

DIC(Disable Interrupt on Completion) |

该位置1,防止IDMA状态寄存器的TI/RI位置1。

|

0 |

RES |

/

|

DES1用于配置每个描述符的数据长度,说明如下:

位域 |

位域名称 |

说明 |

|---|---|---|

31:26 |

RES |

/

|

25:13 |

BS2(Buffer 2 Size) |

缓存2容量

该位表示第二数据缓存的字节容量。缓存容量一定是2的整数倍,对应总线位宽。

如果缓存容量不是2的整数倍,会造成未定义的结果。

如果该位域为0,DMA忽略该缓存,跳到下一个双缓存结构的缓存。

对于链式结构,该位域是无效的;此时DES0[4]置1。如果在任意的描述符里该位被设置为0,

那么剩下的描述符不能为非零值,直到最后一个描述符。

|

12:0 |

BS1(Buffer 1 Size) |

缓存1容量

表示数据缓存的字节容量,它一定是2的整数倍,对应总线位宽。

如果缓存容量不是2的整数倍,会造成未定义的结果。该位域不能为0。

注意:如果仅有一个缓存被编程,必须使用缓存1,而不是缓存2.

|

DES2用于配置第一个描述符的起始地址,说明如下:

位域 |

位域名称 |

说明 |

|---|---|---|

31:0 |

缓存地址指针1 |

当使用双缓存结构时,该位表示第一个数据缓存的物理地址。对于链式结构,该位域表示数据缓存的物理地址。

|

DES3用于配置下一个描述符的起始地址,说明如下:

位域 |

位域名称 |

说明 |

|---|---|---|

31:0 |

缓存地址指针2 |

当使用双缓存结构时,该位域表示第二个缓存的物理地址。如果DES0[4]置1,该地址指向下一个描述符的地址。如果不是最后一个描述符,下一个描述符的地址一定要总线位宽对齐,即bit[2:0]为0,对应总线位宽为64/32/16,内部最低有效位被忽略。

|

IDMA控制器初始化

写IDMAC总线模式寄存器(PBUSCFG),设置Host总线访问参数;

写IDMAC中断使能寄存器(IDMAINTEN),屏蔽掉不需要的中断;

驱动软件创建发送或接收的描述符链表,并写入IDMAC描述符链表基址寄存器(IDMASADDR),为IDMAC提供起始地址;

IDMAC模块从描述符链表获取描述符。

8.1.2.3. 卡接口模块

卡接口模块连接总线接口模块和SD/MMC Card或SDIO设备。Host向HIF的控制寄存器写入命令参数,这些参数发送到CIF。 根据控制寄存器的值,CIF生成命令和数据,根据不同的设备协议,在响应的总线上进行传输。 为了使CIF正确的工作,软件必须满足如下要求:

对于命令和数据传输,同一时间仅选择一个Card;

同一时间仅能发送一个命令;

对于开放式的写操作,如果因为FIFO为空Card时钟停止了,软件必须向FIFO填满数据,才能启动时钟;

对于SDIO传输,如果Card功能挂起,软件想要恢复挂起的传输,在发送新的数据传输命令时,必须复位FIFO并发送恢复命令;

当Card正在处理数据传输时,发送卡复位命令(CMD0,CMD15或CMD52),软件必须设置命令寄存器的stop_abort_cmd位,确保发送复位命令之前先停止数据传输;

当OINTST寄存器的EBE置位,控制器不能保证SDIO中断。软件应该忽略SDIO中断,发送停止或丢弃命令给Card,确保Card停止发送读数据;

在读数据时,如果Card时钟因为FIFO满而停止,软件应该继续读至少两个FIFO地址,再启动Card时钟。

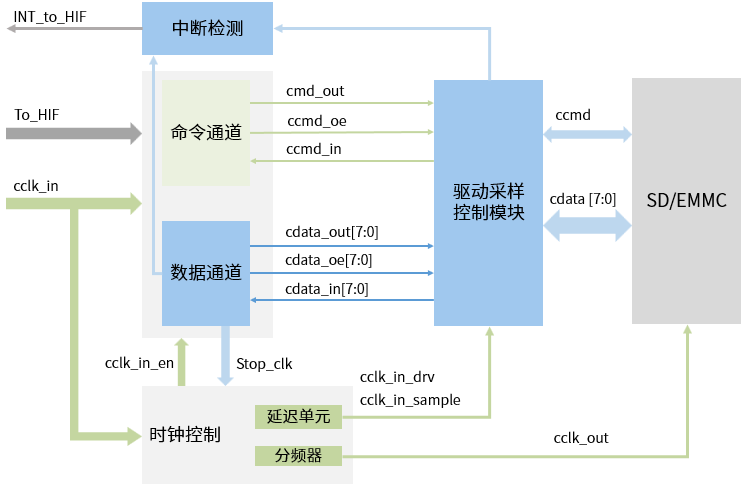

CIF模块主要包括命令通路,数据通路,SDIO中断控制,时钟控制,复用/去复用单元等,框图如下:

命令通道

主要功能:

加载时钟参数

加载Card命令参数

发送命令到Card总线

从Card总线接收设备响应

发送响应到HIF

通过对HIF寄存器编程发送一个新的命令,将命令寄存器的start_cmd位置1。HIF的start_cmd有效,表示新的命令被发送。 命令通路加载新的命令,并发送一个应答信号给HIF,此时cmd_taken信号有效。

命令加载后,命令通路的状态机发送命令给SD/MMC总线,包括内部产生的CRC7校验码,并接收Device返回的响应数据。 然后,状态机发送接收的响应数据和命令完成的信号(CCS)给HIF,并等待8个时钟周期,再加载新的命令。

数据通道

数据通路模块在写数据时,从FIFO中取出数据通过cdata_out发送数据;在接收数据时,通过cdata_in将接收到的数据送入FIFO。 数据通路加载新的数据参数,包括是否传输数据,读或写数据传输方向,流传输或块传输方式,数据块容量,字节数量,Card类型,超时时间等。

如果命令寄存器的data_expected位置1,新的传输命令会根据如下情况在数据通道执行:

如果read/write位为1,发送数据;

如果read/write位为0,接收数据;

SDIO中断控制

SDIO设备的中断请求报告给HIF,经过两个时钟周期,中断信号有效。SDIO设备在中断周期内通过保持cdata_in为低有效产生中断信号。 通过中断控制状态机决定被选择的设备工作在中断周期内。对于不活动或未选择的设备,或工作在1位数据模式下,中断周期总是有效的。 对于工作在宽总线模式,活跃的或被选中的设备需要满足以下条件,中断周期才是有效的:

设备空闲时产生中断;

没有正在处理的数据传输命令时产生中断;

在两个数据块之间的结束位之后的第三个时钟产生中断;

上一笔数据结束位之后的两个时钟到下一笔数据命令的结束位期间产生中断。

备注

当Card数据总线为4位时,在以下情况下,控制器不会采样被选中卡的SDIO中断。因为SDIO中断为电平触发,它需要在一个中断周期内进行采样,host才不会丢失任何来自卡的中断。

读或写恢复:CIF将恢复命令当作正常的数据传输命令处理。SDIO中断在恢复命令处理时,与其他数据命令类似。 根据SDIO协议,对于正常的数据命令,在命令结束位之后中断周期结束。对于恢复命令,在响应结束位之后中断周期结束。 在恢复命令的结束位之后,停止中断采样。

读数据期间挂起:如果读数据传输被Host挂起,Host将abort_read_data位置1并复位数据状态机。 在CIF中,从恢复命令响应到abort_read_data位置1期间,SDIO中断不会被采样。 在Host将abort_read_data位置1后,SDIO中断被处理,启动中断采样。

时钟控制

时钟控制模块提供了不同的时钟频率来满足SD/MMC不同速度模式下的频率要求。cclk_in信号是源时钟(频率大于等于Card最大工作时钟频率), 它经过时钟分频器分频。源时钟用于产生不同的Card时钟频率cclk_out。每个Card时钟可以拥有不同的时钟频率, 因为SD Card可以是低速卡或高速卡。每个Card都提供了一个时钟信号,允许每个卡工作在不同的时钟频率。

错误检测

响应错误:

响应超时:计时器到达超时寄存器配置的超时时间后,未接收到响应的起始位。

响应CRC错误:收到期望的响应并检查响应数据的CRC校验码,响应数据中的CRC7校验码与内部生成的校验码不匹配。

响应错误:响应的传输位不为0,命令序列与发送的命令序列不匹配,或响应的结束位不为1。

数据发送错误:

无CRC状态信号:在一个写数据期间,如果在数据块发出之后的2个时钟周期后,CRC状态信号的起始位没有接收到,产生无CRC状态的错误。

无效的CRC:如果在写数据块发送之后产生无效的CRC状态(非010),一个数据CRC错误信号会发送到HIF,数据传输继续进行。

由于FIFO为空造成的Data Starvation:如果在写数据时FIFO为空,或Card时钟停止且数据超时后FIFO剩余的数据为空,一个data-starvation信号会发送到HIF单元,数据通道继续等待数据进入FIFO。

数据接收错误:

数据超时:在读数据时,如果计时器到达超时时间后,没有接收到数据的起始位,会发生数据超时错误。

数据起始位错误:在4位或8位模式读数据时,如果发生起始位错误,应用程序必须发送CMD12或CMD52结束错误状态。在命令接收完成后,应用程序必须复位IDMAC和CIF,并清除错误状态。发送任意的数据传输命令之前FIFO必须复位。

数据CRC错误:在读数据块传输期间,如果接受到的CRC16校验码与内部产生的CRC16校验码不匹配,数据通道发送数据CRC错误的信号给HIF,继续传输数据。

数据结束位错误:在读数据期间,如果接收到的数据结束位不为1,数据通道发送end-bit错误信号给HIF,并终止数据传输,该信号发送HIF则数据传输完成。

由于FIFO满造成的Data starvation:在读数据传输期间,当FIFO为满,Card时钟停止。如果FIFO满并且数据超时,data starvation错误信号发送到HIF(此时OINTST寄存器的Host-Timeout位置1),数据通道继续等待FIFO变为空。

如果在读操作时Card时钟因为FIFO满而停止,Host控制器不能正确的采样到数据。

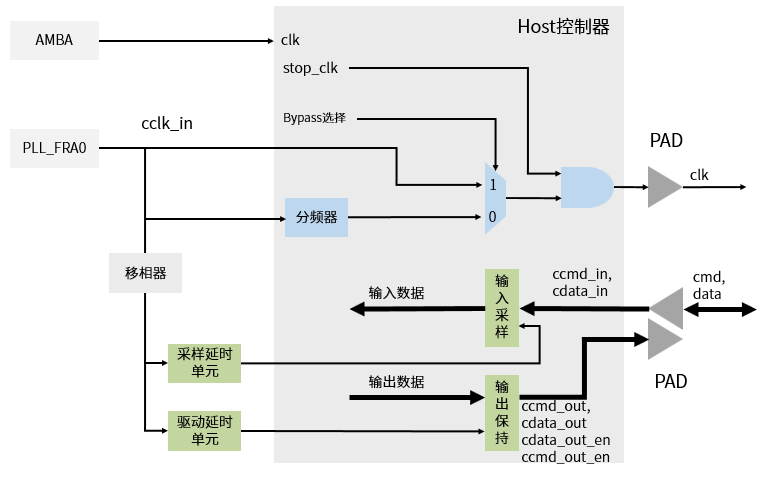

8.1.2.4. 时钟和时序

时钟域

在控制器内部,有多种不同的时钟域,各个时钟域之间的关系描述如下:

clk-系统/Host/AHB总线时钟:HIF模块使用该时钟,所有的配置寄存器使用该时钟。

cclk_in-输入时钟:CIF模块大部分模块和寄存器工作在该时钟的上升沿,时钟Gate信号用来Gate输出到卡的时钟,使用输入时钟的下降沿进行Gate。

cclk_in_drv-驱动时钟:输入时钟经过相位移动和延迟单元输出的驱动时钟,用于数据和命令的输出驱动。该时钟用来满足不同速度模式下保持时间的要求。

cclk_in_sample-采样时钟:输入时钟经过相位移动和延迟单元输出的采样时钟,用于数据和命令接收采样。

cclk_out-输出时钟:由cclk_in分频后输出给卡的工作时钟。

控制器时钟域框图如下:

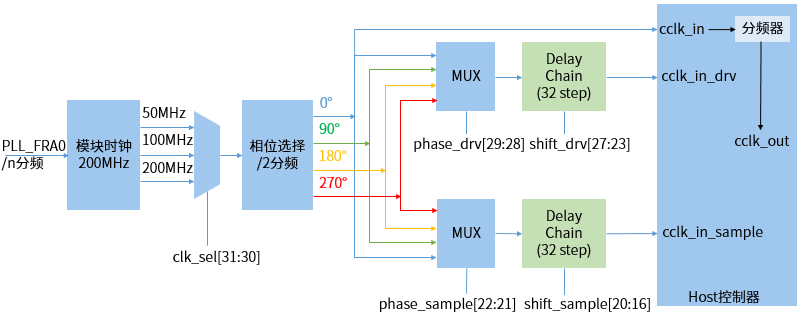

延时控制

由于控制器内部由多种不同的时钟组成,输出驱动时钟和采样时钟需要经过一个相移器和延迟单元进行延迟,以满足不同速度等级的SD/MMC设备稳定的工作时序要求。 因此,需要在Host控制器外部实现相移和延迟电路。结构框图如下:

在CMU模块对PLL_FRA0进行分频,输入到Host控制器的模块时钟频率最大为200MHz,经过时钟选择复用器选择控制器输入时钟,再经过内部时钟分频器clk_divider0进行分频后输出, 以满足不同的速度等级要求,共有3种选择:

2b’00:25MHz,对应速度模式:DS,HS-SDR,HS-DDR

2b’01:50MHz,对应速度模式:HS,HS-SDR,HS-DDR

2b’10:100MHz,对应速度模式:HS-DDR

速度模式等级说明:

DS:SD卡默认速度模式,工作电平3.3V,工作频率0~25MHz,最大传输速率25Mbps;

HS:SD卡高速模式,工作电平3.3V,工作频率0~50MHz,最大传输速率50Mbps;

HS-SDR:eMMC高速SDR模式,工作电平3.3V,工作频率0~50MHz,最大传输速率50Mbps;

HS-DDR:eMMC高速DDR模式,工作电平3.3V,工作频率0~50MHz,最大传输速率100Mbps。

经过时钟复用器选择后,进入移相器,共有4种相位可编程:0°,90°,180°,270°。每个相位之后再经过一级Delay Chain进行32级的延迟, Delay Chain内部由若干个延时单元组成,每个延时单元的延时时间相同。未经过相位延迟和delay chain的时钟作为控制器的输入时钟cclk_in, 经过控制器内部的分频器分频输出cclk_out,作为外设的接口时钟。用户可以通过SMC_DLYCTRL寄存器对时钟相位,Delay Chain进行编程选择。