11.1.2. 功能描述

11.1.2.1. PHY接口选择

此USB Device模块支持UTMI接口,UTMI接口对应的采用内部PHY0。UTMI接口的相关配置采用默认值即可,无需配置。

11.1.2.2. FS/HS设备选择

此USB Device模块支持作为FS或HS设备,通过USB_DEV_SPD_SET可进行配置,默认为HS设备。这里的配置需要在初始化完成,完成后,通过PHY即可以实现相应的端接电阻配置。

11.1.2.3. 枚举地址设置

在USB的枚举过程,USB Host会通过Set Address命令对USB Device的地址进行枚举,枚举地址需在USB_DEV_ADDR设置。

11.1.2.4. 中断

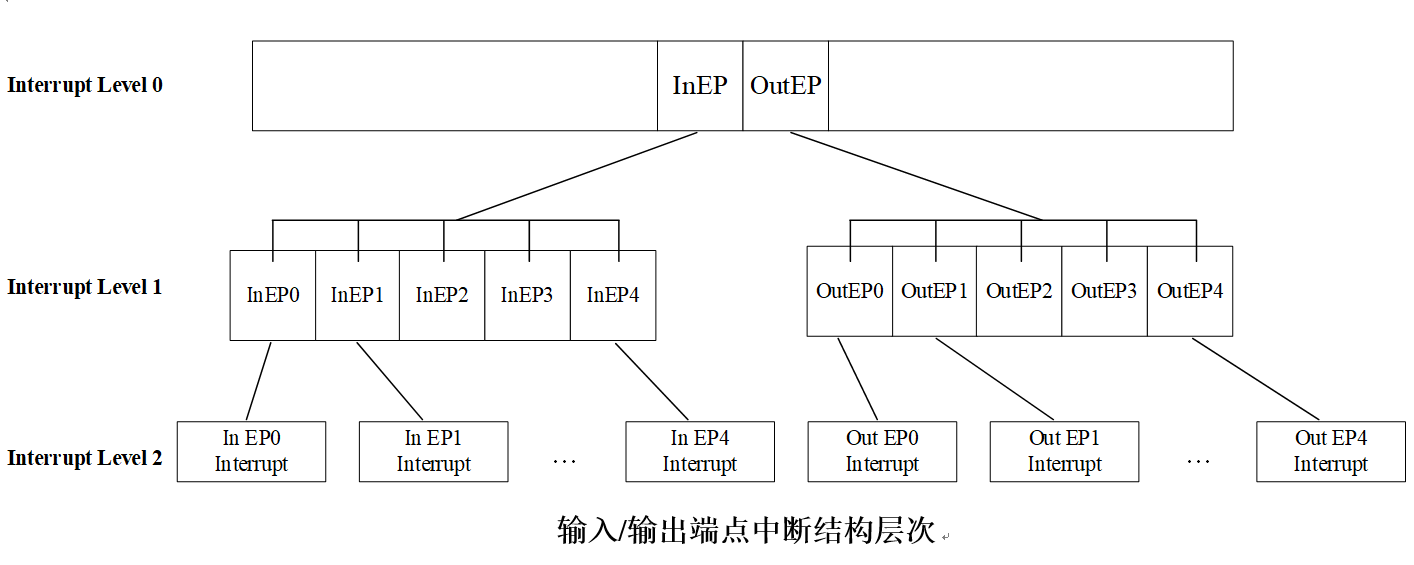

USB Device模块支持中断,对应的中断会有中断屏蔽控制,默认是所有的中断均屏蔽,需要根据不同应用场景,进行将中断信号使能。其中IN/OUT端点的中断信号存在层次结构的逻辑关系,如下图所示。

在Interrupt Level 0的InEP和OutEP中断,分别为所有IN端点和所有OUT端点的总中断状态,此位不能写1清除,只能通过把所有端点产生的中断态进行清除,才可清除。

InEP和OutEP的下一层次的逻辑分别是InEP0/InEP1/…/InEP4和OutEP0/OutEP1/…/OutEP4,这里都是各个端点的总中断态,可以通过屏蔽寄存器对某个端点的总中断态屏蔽,默认是对所有的端点的中断态屏蔽。此层次的中断也不可通过写1清0,只有清除下一层次的所有中断态才可以清除此层次的中断。

Interrupt Level 2是IN/OUT端点的具体中断态,这个层次的中断的屏蔽控制,InEP共用一套屏蔽控制逻辑,由INEP_INT_MSK决定,默认是屏蔽所有的中断态,OutEP相同的,也是共用一套屏蔽控制逻辑,由OUTEP_INT_MSK决定,默认是屏蔽所有的中断态。

图 11.3 输入输出端点的中断结构层次

11.1.2.5. DMA控制

USB Device控制器可以通过EN_DMA,配置FIFO的读取方式。

EN_DMA = 0(默认值),FIFO的读取方式为通过AHB总线进行FIFO数据的读写,需要软件介入控制读写过程。

EN_DMA = 1,使能DMA,FIFO的读取方式为通过DMA进行FIFO数据的读写,无需软件介入读写过程。若采用DMA的方式,需注意FIFO的末端地址的保留,具体参见下一节的说明。

采用DMA进行读写数据,只需配置将接收/发送数据的Buffer地址,写入端点相应的DMA地址,DMA会根据接收/发送数据的长度,读取RXFIFO的数据或者往TXFIFO里写入数据。

11.1.2.6. 数据FIFO

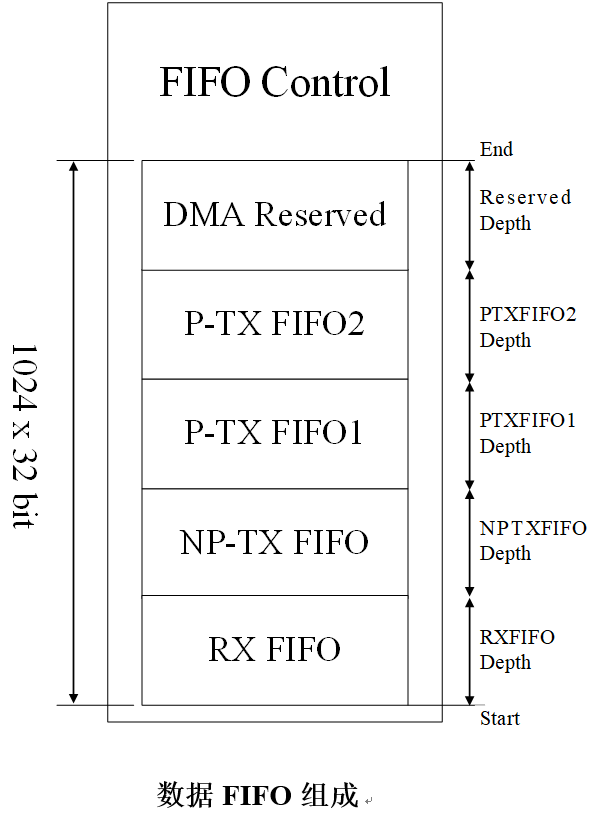

USB Device的数据FIFO总的深度为1024 x 32bit,FIFO的组成如下图所示。

DMA Reserved部分为在USB Device采用内部DMA的时候需要保留,即FIFO的末端的10 x 32bit的空间为DMA所用,不能作为其他功能的FIFO所用。在未采用内部DMA的时候,此部分无需保留,可以用于其他功能。

FIFO的起始为RXFIFO,紧接着依次为NP-TXFIFO(非周期的TXFIFO)、P-TXFIFO1(周期的TXFIFO1)、P-TXFIFO2(周期的TXFIFO2)。RXFIFO为所有OUT EP的共用FIFO,NP-TXFIFO为所有的Control/Bulk类型的IN EP的共用FIFO,P-TXFIFO1、P-TXFIFO2用于Interrupt/Isochronous类型的EP对应FIFO,若无使用到此类型的EP可以设置该FIFO深度为0。

通过FIFO对应的FIFO深度寄存器配置各个FIFO的大小,如果不需要则可以配置为0深度。

图 11.4 数据FIFO组成

11.1.2.7. 接收控制

所有的OUT端点共用RXFIFO,所有OUT端点的接收方式都相同,RXFIFO的读取基地址为(BASE_USB0 + 0x1000)。接收的流程如下:

中断RxFLvl产生,指示RXFIFO接收了至少一个数据包,注意此中断状态位为只读。

此时可以通过读取RXFIFO_STS_POP寄存器,将接收到的数据POP到端点相应的FIFO的起始地址(BASE_USB0 + 0x1000)。因此其他非接收数据操作时,不允许对此寄存器进行读操作,避免造成接收数据的错误。

通过读取RXFIFO_STS_POP寄存器可知接收数据的状态、接收到数据的Byte数量、端点号、数据PID类型等信息。

如果接收数据的状态是接收到OUT数据包或SETUP数据包,那么就可以读取相应端点的FIFO起始地址,每次读出4Byte数据,根据获取的Byte总数决定读取的次数,每次读FIFO的起始地址即可。

如果USB Device模块设置为DMA模式,那么上述的操作可以忽略,DMA自动完成读数据的操作。

11.1.2.8. 发送控制

控制类型端点的发送流程如下(即IN EP0的发送数据流程):

使能NP_TXFIFO_EMP中断。

当NP-TXFIFO半空或空(可通过寄存器NP_TFTH配置选择)的时候中断产生,对端点相应的FIFO的起始地址进行写数据,每写一次完成4Byte的数据写入FIFO,每次只需对FIFO的起始地址(BASE_USB0 + 0x1000)写即可,写的次数取决与需要发送的数据长度。

完成数据的写入后,需要屏蔽NP_TXFIFO_EMP中断,以备下一次的数据发送。

如果USB Device模块设置为DMA模式,那么上述的操作可以忽略,DMA自动完成写数据的操作。

Bulk类型端点的发送流程如下(即IN EP1~4的发送数据流程):

初始化需对此端点的RX_INTOKEN_EMPTY_INT中断使能,即对应的端点收到IN Token后则产生中断。

当ITTXFE中断到来,对端点相应的FIFO的起始地址进行写数据,每完成一次4Byte的数据写入FIFO,每次只需对FIFO的起始地址(BASE_USB0 + 0x1000 * (n+1), n = 1/2/3/4)写即可,写的次数取决与需要发送的数据长度。

完成数据的写入后,对RX_INTOKEN_EMPTY_INT中断写1清除中断态,完成一次的写数据。

如果USB Device模块设置为DMA模式,那么上述的操作可以忽略,DMA自动完成写数据的操作。

11.1.2.9. 端点控制

通过寄存器IN_EPn_CFG以及OUT_EPn_CFG可对IN/OUT端点进行以下的操作:

使能端点EP

设置EP的类型(Bulk/Interrupt/Iso)

在当前配置下激活端点EP

设置最大数据包大小

选择TXFIFO的编号(针对IN EP)

设置Data0/Data1 PID

设置NAK

设置STALL

设置接收或发送Transaction时所对应的奇/偶帧