11.5.1. 概述

UART是一种与外围设备、数据载体设备、或者数据集等进行串行通信的接口。主处理器(CPU)通过APB总线将数据写到UART,数据转换成串行形式后传输到目标设备。UART也可以接收串行数据和存储,以供主处理器(CPU)读取。

UART包含着控制字符长度、波特率、奇偶校验以及生成中断的寄存器。尽管UART只有一个中断输出信号,但有几种优先级的中断类型可响应,每种中断类型都可以通过控制寄存器单独使能/未使能。

UART有16450以及16550两种工作模式,因此可与一系列标准软件驱动程序兼容。在16550模式中,数据的发送与接收都由FIFO缓存;而在16450模式中是禁用这些FIFO的。

UART支持5-8位的字长,一个可选的奇偶校验位,1/1.5/2个停止位,可通过CPU APB接口编程,包含16位可编程波特率发生器和8位暂存器,以及独立的发送和接收FIFO。提供八条调制解调器控制线和调试回环模式。

中断可在发送缓冲/FIFO、接收缓冲/FIFO、调制解调器状态以及线路状态范围内生成。

11.5.1.1. 特性说明

兼容工业标准16550 UART

256x8bit发送与接收FIFO

传输速度可达3Mbps

支持5-8数据位以及1/1.5/2停止位

支持奇校验,偶校验或者无奇偶校验

支持DMA控制器接口

支持软件/硬件流控

支持RS-485 9bit 模式

支持RS-485硬件自动控制收发方向

11.5.1.2. 原理框图

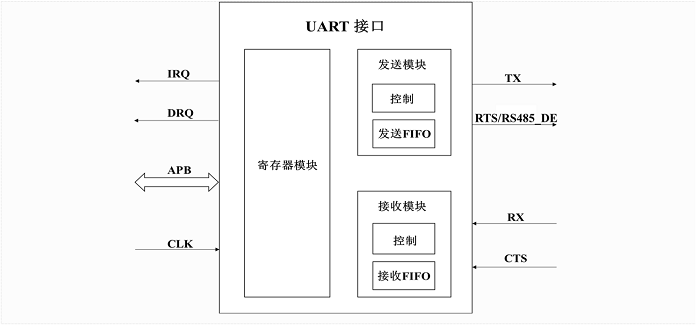

UART原理框图如图所示:

图 11.9 UART 原理框图