11.9.2. 功能描述

11.9.2.1. 总线时序与配置说明

以下所述的时钟周期,均是指内部PBUS CLK的周期,PBUS CLK从HCLK时钟分频得到,通过配置CLK_DIV字段可以从HCLK进行2/4/8分频。

PBUS每个信号含义如下表所示

信号名称 |

输入/输出 |

信号描述 |

|---|---|---|

CLK |

O |

外部总线时钟信号

被访问外设不需要时钟信号,工作在异步模式;

被访问外设需要时钟信号,则工作在同步模式。

|

NCS |

O |

外设片选信号,默认低电平有效

|

NADV |

O |

总线地址有效信号,默认低电平有效

电平为低时,指示AD[15:0]为地址

|

NWE |

O |

总线读写控制信号

默认低电平为写,高电平为读

|

NOE |

O |

外设输出使能信号,默认低电平有效

有效时允许外设往AD[15:0]输出读数据信号

|

AD[15:0] |

I/O |

地址/数据总线

此总线16bits宽,地址与数据复用,并且可传输读写双向数据

可访问地址空间为64K,映射地址为0x1080_0000~0x1080_ffff

|

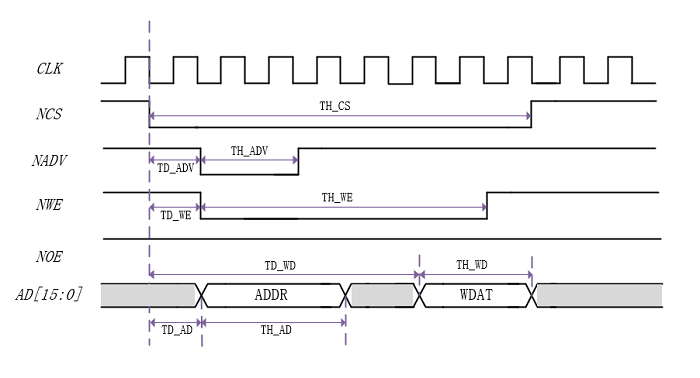

如下面的时序图所示,对于每一个信号可调整的参数有THxx,表示该信号保持的BUS CLK周期数;TDxx表示该信号有效时刻点相对NCS有效时刻点的延迟。

如图 写时序举例 ,给出了一种参数配置:TH_CS=8,TD_ADV=1,TH_ADV=2,TD_WE=1,TH_WE=6,TD_AD=1,TH_AD=3,TD_WD=6,TH_WD=2。具体输出时序可以通过调整以上参数进行灵活配置。

但是必须注意:a)THxx参数不允许为0;b)WDAT必须在ADDR结束后才有效,即TD_WD≥TD_AD+TH_AD。

图 11.66 写时序举例

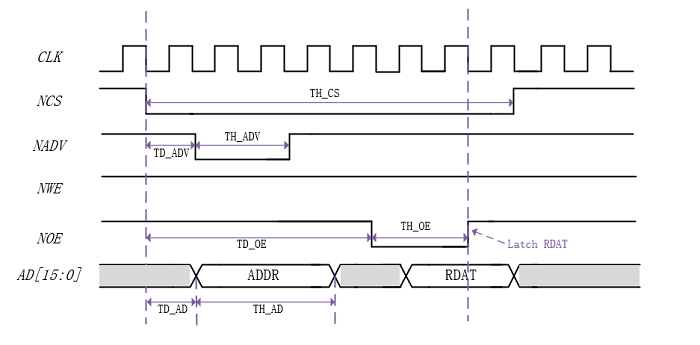

如图 读时序举例 所示,与上面“写时序图举例”的差异就在于NOE信号,TD_OE=5,TH_OE=2。

读操作时注意,a) NOE信号有效区间不能与AD[15:0]输出有效区间相重叠,即TD_OE≥TD_AD+TH_AD;b)保证TD_OE > TD_ADV+TH_ADV;c) PBUS模块对于AD[15:0]上RDAT的采样发生在NOE信号有效的最后时刻。

图 11.67 读时序举例

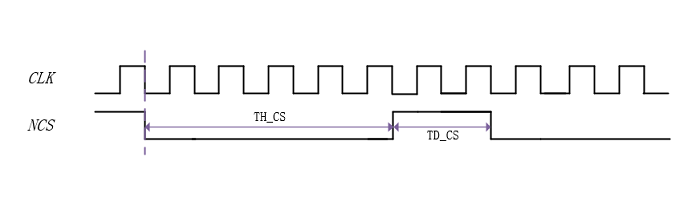

如图 两次操作之间的最小延迟 所示,NCS信号除了有一个TH_CS参数之外,还有一个规定了两次NCS有效的最短时间间隔参数TD_CS,表示两次传输之间必须保持一定的间隔,目的是为了避免两次传输之间AD[15:0]信号冲突。

图 11.68 两次操作之间的最小延迟

11.9.2.2. 模块工作流程

写操作:

- Check TD_CS →

NCS有效 → Check TH_CS → NCS无效

Check TD_ADV → NADV有效 → Check TH_ADV → NADV无效

Check TD_WE → NWE有效 → Check TH_WE → NWE无效

Check TD_AD → ADDR输出 → Check TH_AD → 关闭ADDR输出,同时Check TD_WD → WDAT输出 → Check TH_WD → 关闭WDAT输出

读操作:

- Check TD_CS →

NCS有效 → Check TH_CS → NCS无效

Check TD_ADV → NADV有效 → Check TH_ADV → NADV无效

Check TD_AD → ADDR输出 → Check TH_AD → 关闭ADDR输出,同时Check TD_OE → NOE有效 → Check TH_OE → NOE无效,同时锁存RDAT

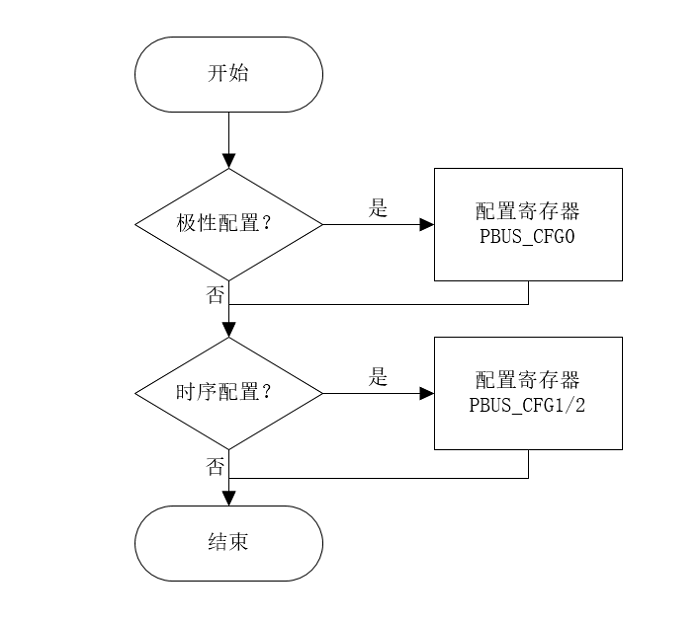

11.9.2.3. 使用指南

寄存器PBUS_CFG0、PBUS_CFG1、PBUS_CFG2的默认值已经可以直接使用,用户通常只需要使能CMU模块时钟以及松开复位,PBUS即可通过映射地址空间0x1080_0000~0x1080_ffff进行PBUS外设的读写访问