11.3.2. 功能描述

11.3.2.1. RMII/RGMII接口选择

此GMAC模块可以通过SYSCFG的GMAC配置寄存器,选择配置成RMII接口或RGMII接口。 RMII接口对应连接百兆网口PHY,支持100M/10M Link速度; RGMII接口对应连接千兆网口PHY,支持1000M/100M/10M Link速度。

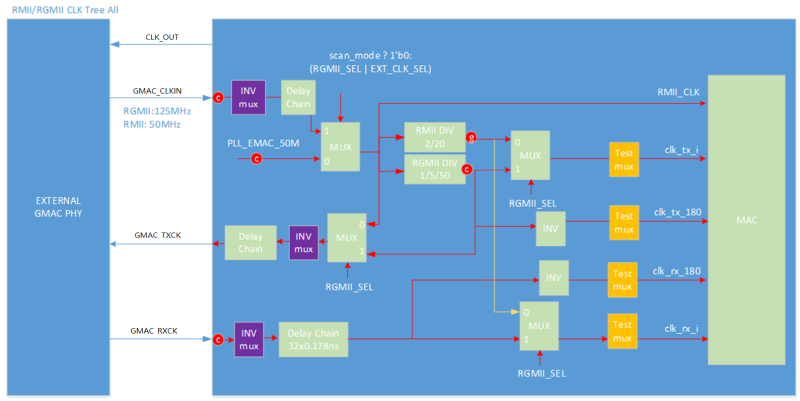

11.3.2.2. 时钟树

图 11.7 GMAC Clock Tree

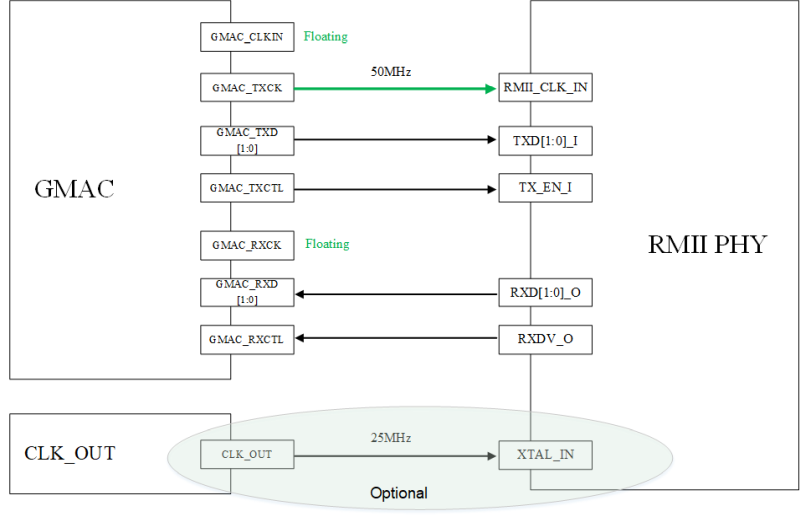

11.3.2.2.1. RMII接口时钟选择

MAC提供参考时钟

MAC提供50MHz时钟源至外部PHY,如下图所示,其中CLK_OUT可以输出25MHz替代PHY的外部晶振,取决于用户使用。

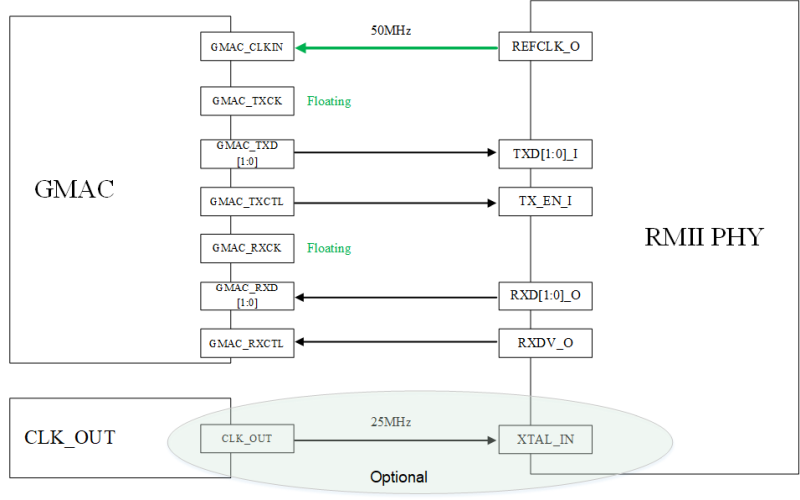

PHY提供参考时钟

MAC接收PHY提供的RMII 50MHz参考时钟源,如下图所示,其中CLK_OUT可以输出25MHz替代PHY的外部晶振,取决于用户使用。

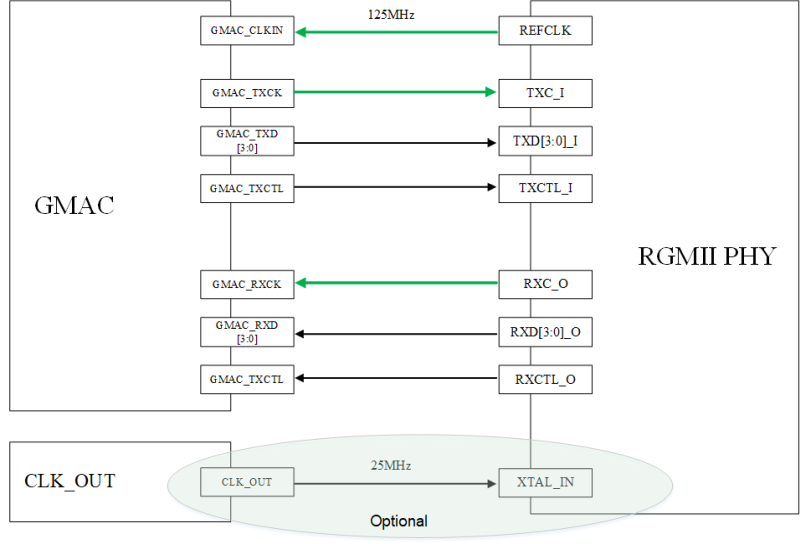

11.3.2.2.2. RGMII时钟选择

仅支持MAC接收PHY提供的RGMII 125MHz参考时钟源的情况,如下图所示,其中CLK_OUT可以输出25MHz替代PHY的外部晶振,取决于用户使用。

11.3.2.3. MDIO

GMAC通过MDIO(Management Data In/Out)接口,可以对PHY的寄存器进行读写操作,进而控制PHY的工作模式以及获取PHY的工作状态。操作MDIO接口,可以操作寄存器MDIO_CTL和MDIO_DAT实现。

MDIO接口由MDC以及MDIO实现:

MDC,时钟输出信号,提供给PHY,需要根据D211 AHB0总线的时钟来配置时钟分频系数获得,具体配置见寄存器MDIO_CTL描述;

MDIO,数据输入输出信号,MDIO的帧的格式为:Idle + Preamble + Start + Opcode + Phy Addr + Reg Addr + TA + Data。

MDIO帧域 |

描述 |

|---|---|

IDLE |

IDLE域 |

PREAMBLE |

32个连续的Bit 1 |

START |

标志帧的起始位置,2’b10 |

OPCODE |

操作标识域,2’b10表示读,2’b01表示写 |

PHY ADDR |

5-bit的PHY地址域 |

REG ADDR |

PHY寄存器地址 |

TA |

Turnaround域,读操作为2’bZ0,写操作为2’b10 |

DATA |

16 bit数据,读操作MAC为接收数据,写操作MAC为发送数据。 |

11.3.2.4. MAC发送功能

SA源地址自动插入或替换功能

配置MAC_TX_FUNC寄存器[14:12],MAC TX支持自动插入或替换发送帧的源地址,源地址可通过寄存器MAC_ADDR0或MAC_ADDR1配置。

TX Jabber Timer

MAC TX支持Jabber Timer,用于检测发送的帧长度,若关闭Jabber Timer,发送帧的长度可以达到16383 bytes;若未关闭Jabber Timer的功能,最多只能发送2048 bytes(使能Jumbo Frame后,最大发送的长度为10240 bytes),并且会在TDES0的BIT14置1,指示发送的数据过长,发生Jabber Timeout。

CRC 插入/替换

配置TX DMA描述符TDES0 [27],可以对发送帧进行CRC的插入;

配置TX DMA描述符TDES0 [24],可以对发送帧进行CRC的替换,此时需要设置TDES0[27] = 1,关闭CRC的插入功能。

自动补0

配置TX DMA描述符TDES0 [27],可以对长度低于64 bytes的发送帧进行自动补0,并且此时会强制产生4 bytes的CRC,即short frame + 0 pad + CRC = 64 bytes。若不需要进行自动补0,可以设置TDES0[27] = 1。

TX IP校验和插入

MAC支持对发送帧的IP校验和进行计算和插入,通过配置MAC_CFG[7] = 1,打开IP Offload功能,然后通过TDES0[23:22]选择IP检验和的计算类型,MAC支持IP header校验和、IP Payload校验和以及伪header校验的硬件加速计算;

另外打开IP Offload功能后,TDES0[16]可以指示发送帧的IP校验和是否正确,置1表示发送帧存在IP校验和错误。

11.3.2.5. MAC接收功能

地址过滤

对于接收帧,MAC可以进行地址过滤,包括:

单播地址过滤

源地址过滤

反向源地址过滤

目的地址过滤

反向目的地址过滤

广播地址过滤

多播帧过滤

控制帧过滤

另外,RDES0[30]、[13]分别指示接收帧的目的地址、源地址过滤是否成功。

RX Watchdog

MAC RX支持RX Watchdog,用于检测接收的帧长度,若关闭RX Watchdog,发送帧的长度可以达到16383 bytes;若未关闭RX Watchdog的功能,最多只能接收2048 bytes(使能Jumbo Frame后,最大接收的长度为10240 bytes),并且会在RDES0 [4]置1,指示接收的数据过长,发生Watchdog Timeout。

CRC/PAD剥离

MAC支持对接收帧进行CRC/PAD剥离:

配置EN_STRIP_FCS = 1,可以对长度≥1536 bytes的接收帧进行CRC剥离;

配置EN_STRIP_NML = 1,可以对长度<1536 bytes的接收帧进行CRC以及PAD剥离。

RX IP校验和计算

MAC支持对接收帧的IP校验和进行计算,通过配置MAC_CFG[7] = 1,打开IP Offload功能。此时需要设置ALT_DES_SIZ = 0x1,激活RDES4的状态,软件通过RDES4可以获取接收帧IP检验和的校验结果,从而得知接收的IP帧的校验和结果。

11.3.2.6. 流控

流控功能包括如下,可通过寄存器FLOW_CTL控制:

TX流控

在全双工模式下,支持Pause帧的发送

在半双工模式下,支持背压操作

RX流控

支持Pause帧的解析,以及停止发送约定的Pause时间

单播Pause帧

MAC模块支持单播的Pause帧

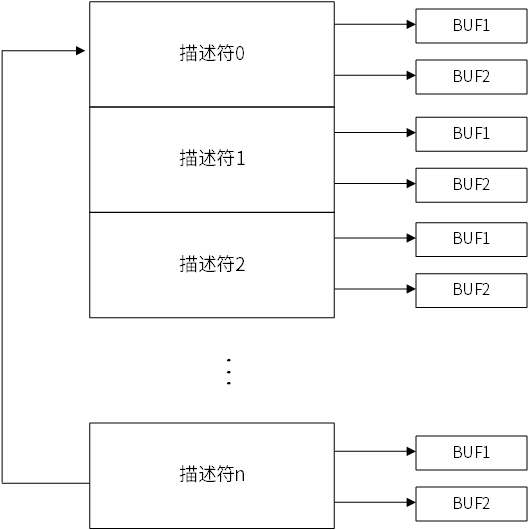

11.3.2.7. DMA结构

GMAC内部具有DMA,用于将发送BUFFER(DRAM地址)的数据传送到TXFIFO, RXFIFO接收到的数据传送到接收BUFFER(DRAM地址)。DMA可以支持两种结构,分别是环型结构和链型结构。

11.3.2.7.1. 环形结构

环型结构(Ring)的描述符,可以通过DES_SKIP_LEN来配置设定,两两描述符之间的跳跃长度,而另外通过描述符的START_DES和END_DES来决定环形结构的第一个描述符和最后一个描述符,从而形成环路。

11.3.2.7.2. 链型结构

链型结构(Chain)的描述符,则通过描述符的Next Descriptor Address来进行指向连接,在最后一个描述符的Next Descriptor Address域上设置为第一个描述符地址,此时也同样形成环路。

11.3.2.8. DMA发送描述符

注意:发送描述符TDES4~7(TDES4~5 Reserved,TDES6~7 时钟戳信息)的应用,需要设置寄存器DMA0/1_CONF的ALT_DES_SIZ = 1。

11.3.2.8.1. 发送描述符TDES0

Bit |

域描述 |

|---|---|

31 |

TX_PRC

Transmit in Process,发送进行中。

0x0:DMA空闲,DMA完成当前的描述符的数据发送

0x1:DMA发送进行中

|

30 |

EN_TX_COMP_INT

Enable Transmit Complete Interrupt,使能发送完成中断,此位只有在BIT29有效时才有效。

0x0:未使能

0x1:使能,此位只有在BIT29有效

|

29 |

END_DES

End Descriptor,最后一个描述符。

0x0:无效

0x1:有效,表示此描述符为最后一个描述符

|

28 |

START_DES

Start Descriptor,第一个描述符。

0x0:无效

0x1:有效,表示此描述符为第一个描述符

|

27 |

DIS_CRC

Disable CRC,禁止CRC功能,这里生效,只需在第一个描述符设置此位即可。

0x0:无效

0x1:有效,禁止CRC

|

26 |

DIS_PAD

Disable Padding,禁止补0功能,这里生效,只需在第一个描述符设置此位即可。

0x0:无效

0x1:有效,禁止对帧长低于64 bytes进行补0

|

25 |

EN_TX_TMSTMP

Enable Transmit Timestamp,使能发送添加时间戳功能。

0x0:未使能

0x1:使能

|

24 |

EN_CRC_REP

Enable CRC Replacement,使能CRC替代功能。这里需要软件保证发送帧的内容包含了CRC,使能CRC替代功能后,会

进行CRC重新计算并且替代。另外为了避免CRC重复,需要DIS_CRC =1 禁止CRC插入。

0x0:未使能

0x1:使能

|

23:22 |

EN_CIC

Enable Checksum Insertion Control,使能校验和插入功能。

0x0:禁止校验和插入

0x1:开启IP Header校验和计算以及插入功能

0x2:开启IP Header、Payload校验和的计算及插入功能,未开启伪Header的校验和计算

0x3:开启IP Header、Payload校验和的计算及插入功能,并且开启伪Header的校验和计算

|

21 |

TX_END_RNG

Transmit End of Ring,DMA发送环的末端,表示此描述符为DMA发送环的最后一个描述符,结束后跳回起始描述符。

0x0:无效

0x1:生效

|

20 |

EN_DMA_CHN_MOD

Enable DMA Chain Mode,使能DMA Chain模式。

0x0:未使能,采用DMA Ring模式

0x1:使能,采用DMA Chain模式

|

19:18 |

VLAN_TAG_CTL

VLAN Tag Control,VLAN 标签控制。

0x0:无效操作

0x1:删除发送帧中的VLAN标签内容

0x2:插入VLAN标签,标签内容

0x3:替代VLAN标签

|

17 |

TX_TMSTMP_STS

Transmit Timestamp Status,发送时间戳状态,此域只有在最后一个描述符有效。

0x0:无操作

0x1:完成发送时间戳的捕捉,时间戳写入在TDES6和TDES7

|

16 |

IP_HD_ERR

IP Header Error,此位置1表示MAC检测发送的IP报文的Header存在错误。

|

15 |

TXERR_STS

Transmit Error Status,发送错误状态指示位。

0x0:无错误

0x1:出现错误,错误源可能由于BIT16/14/13/12/11/10/9/8/2/1相应的错误状态引起

|

14 |

JAB_TO_ERR

Jabber Timout Error,发送Jabber超时错误,此位只有在Jabber检测功能未禁止的情况下有效。

0x0:无异常

0x1:出现发送超时错误

|

13 |

TXFIFO_FLSH_ERR

TXFIFO Flush Error,清除错误,出现软件清除TXFIFO的帧数据的操作导致的错误。

0x0:无异常

0x1:出现错误状态

|

12 |

IP_PL_ERR

IP Payload Error,此位置1指示MAC检测到发送的TCP、UDP、ICMP IP数据包payload存在错误。

|

11 |

LOS_CR

Loss Carrier,此位置1指示在帧发送发生了载波丢失,此位只有在半双工模式下有效。

|

10 |

NO_CR

No Carrier,此位置1指示在发送的过程中,PHY的载波侦听CS信号并没有生效,即没有检测到载波。

|

9 |

LT_COL

Late Collision,此位置1指示由于碰撞导致发送终止,此碰撞发生在碰撞窗口之后。此位在TXFIFO_UF_ERR = 1的时候

无效。

|

8 |

EXS_COL

Excessive Collision,此位置1指示当前帧尝试发送的过程中,由于连续的16次碰撞的产生终止发送帧。如果取消重传

(DIS_RETRY = 1),只要出现1次的碰撞,此位则立即置1。

|

7 |

VLAN_STS

VLAN Status,VLAN帧状态。

0x0:发送帧为非VLAN帧

0x1:发送帧为VLAN帧

|

6:3 |

COL_CNT

Collision Count,此域指示在发送前发生多少次碰撞。此域在TDES0. Bit8 =1的时候无效。

|

2 |

EX_DEF_ERR

Excessive Deferral Error,发送终止由于回退时间过长,此位只有在EN_DEF_CHECK = 1的情况下有效。

0x0:未发生错误

0x1:出现回退过量错误

|

1 |

TXFIFO_UF_ERR

TXFIFO Underflow Error,TXFIFO下溢出错误,DMA从Buffer地址读取帧数据错误。

0x0:未出现错误

0x1:发生下溢出错误

|

0 |

DEF_STS

Defer Status,回退状态,在发送前检测到载波而引起的回退,此位只对于半双工模式有效。

0x0:未出现回退

0x1:发送时出现回退

|

11.3.2.8.2. 发送描述符TDES1

Bit |

域描述 |

|---|---|

31:29 |

TX_SA_CTL

Transmit Source Address Control,发送源地址控制。

BIT31 = 1,表示采用MAC Address1进行插入或替代;

BIT31 = 0,表示采用MAC Address0 进行插入或替代。

Bit30:29

0x0:无操作

0x1:插入源地址

0x2:替代源地址

0x3:保留

|

28:16 |

TX_BUF2_SIZ

Transmit Buffer2 Size,发送缓存2的空间大小。

|

15:13 |

Reserved

|

12:0 |

TX_BUF1_SIZ

Transmit Buffer1 Size,接收缓存1的空间大小。

|

11.3.2.8.3. 发送描述符TDES2

Bit |

域描述 |

|---|---|

31:0 |

BUF1_ADDR

Buffer1 Address,Buffer1地址指针,Buffer1的物理地址。

|

11.3.2.8.4. 发送描述符TDES3

Bit |

域描述 |

|---|---|

31:0 |

BUF2_ADDR/NXT_DES_ADDR

在DMA采用Ring模式时,这里为BUF2_ADDR,而采用Chain模式时,这里为NXT_DES_ADDR。

BUF2_ADDR

Buffer2 Address,Buffer2地址指针,Buffer2的物理地址。

NXT_DES_ADDR

Next Descriptor Address,下一个描述符的地址,指向下一个描述符的物理地址,从而将描述符连接起来。

|

11.3.2.8.5. 发送描述符TDES6

Bit |

域描述 |

|---|---|

31:0 |

TX_STMP_LO

Transmit Timestamp Low 32bit,发送时间戳的低32位,此域由DMA自动填写,与TDES7的高32bit组成完整的时间戳。

|

11.3.2.8.6. 发送描述符TDES7

Bit |

域描述 |

|---|---|

31:0 |

TX_STMP_HI

Transmit Timestamp High 32bit,发送时间戳的高32位,此域由DMA自动填写,与TDES6的低32bit组成完整的时间戳。

|

注意

发送描述符RDES4~7(RDES4状态信息,RDES5 Reserved,RDES6~7 时钟戳信息)的应用,需要设置寄存器DMA0/1_CONF的ALT_DES_SIZ = 1。

11.3.2.9. DMA接收描述符

11.3.2.9.1. 接收描述符RDES0

Bit |

域描述 |

|---|---|

31 |

RX_PRC

Receive in Process,接收进行中。

0x0:DMA空闲,DMA完成当前的描述符的数据接收

0x1:DMA接收进行中

|

30 |

DA_FLT

Destination Address Filter Fail,目的地址过滤失败。

0x0:无效

0x1:指示接收帧的目的地址过滤失败

|

29:16 |

RX_FRM_LEN

Receive Frame Length,接收到的帧的长度,此域在最后一个描述符有效,并且无异常发生。

|

15 |

RXERR_STS

Receive Error Status,接收错误状态指示位。

0x0:无错误

0x1:出现错误,错误源可能由于RDES0的BIT14/11/7/6/4/3/1或RDES4的[4:3]相应的错误状态引起

|

14 |

RX_DES_ERR

Receive Descriptor Error,接收描述符错误,此域在最后一个描述符有效。

0x0:无效

0x1:由于描述符异常导致的接收中断

|

13 |

SA_FLT

Source Address Filter Fail,源地址过滤失败。

0x0:无效

0x1:指示接收帧的源地址过滤失败

|

12 |

RX_LEN_ERR

Receive Length Error,接收长度错误。

0x0:无效

0x1:指示接收长度错误,接收帧的实际长度与帧的长度域值不一致

|

11 |

RXFIFO_OF_ERR

RXFIFO Overflow Error,接收溢出错误。

0x0:无效

0x1:指示接收溢出错误,由于RXFIFO溢出,导致接收帧的损坏

|

10 |

VLAN_TAG

VLAN Tag,此位置1表示接收的帧位VLAN帧。

|

9 |

START_DES

Start Descriptor,第一个描述符。

0x0:无效

0x1:有效,表示此描述符为第一个描述符

|

8 |

END_DES

End Descriptor,最后一个描述符。

0x0:无效

0x1:有效,表示此描述符为最后一个描述符

|

7 |

TMSTMP_AVL/ IP_CHSM_ERR/ GNT_FRM

此位可指示三种状态:

TMSTMP_AVL,Timestamp Available,置1表示接收的帧已打时间戳,从RDES6~7可获得;

IP_CHSM_ERR,IP Checksum Error,置1表示IP校验和错误或表示接收帧位非IPv4帧;

GNT_FRM,Giant Frame,置1表示接收的帧位Giant Frame。

|

6 |

LT_COL_ERR

Late Collision Error,Late Collision错误。

0x0:无效

0x1:接收发生Late Collision错误

|

5 |

RX_FRM_TYP

Receive Frame Type,接收帧的类型。

0x0:接收帧为IEEE 802.3类型的帧

0x1:接收帧为以太网类型的帧

|

4 |

RX_WD_TO_ERR

Receive Watchdog Timeout Error,接收看门狗的超时错误。

0x0:无效

0x1:发生接收看门狗的超时错误

|

3 |

RX_ERR

Receive Error,接收过程出现RX_ERR信号。

0x0:无效

0x1:接收过程出现RX_ERR信号

|

2 |

Reserved

|

1 |

RX_CRC_ERR

Receive CRC Error,接收CRC错误,此域只有在最后一个描述符有效。

0x0:无效

0x1:接收帧出现CRC错误

|

0 |

EXT_STS_AVA/ RX_MAC_ADDR

EXT_STS_AVA

Extend Status Available,当时钟戳或IP校验和Offload功能使能,此位置1表示RDES4生效。

RX_MAC_ADDR

Rx MAC Address,当时钟戳、IP校验和Offload功能均未使能,此位置1表示接收帧的目的地址匹配MAC

Address1~7之一。此位清0表示接收帧的目的地址匹配MAC Address0。

|

11.3.2.9.2. 接收描述符RDES1

Bit |

域描述 |

|---|---|

31 |

DIS_COMP_INT

Disable Complete Interrupt,禁止接收完成中断的产生。

0x0:未禁止

0x1:禁止

|

30:29 |

Reserved

|

28:16 |

RX_BUF2_SIZ

Receive Buffer2 Size,接收缓存2的空间大小。

|

15 |

RX_END_RNG

Receive End of Ring,指示在DMA的Ring模式下,此描述为最后的描述符,完成后跳转回起始描述符。

|

14 |

RX_DMA_MOD

Receive DMA Mode,接收DMA的模式。

0x0:Ring模式

0x1:Chain模式

|

13 |

Reserved

|

12:0 |

RX_BUF1_SIZ

Receive Buffer1 Size,接收缓存1的空间大小。

|

11.3.2.9.3. 接收描述符RDES2

Bit |

域描述 |

|---|---|

31:0 |

BUF1_ADDR

Buffer1 Address,Buffer1地址指针,Buffer1的物理地址。

|

11.3.2.9.4. 接收描述符RDES3

Bit |

域描述 |

|---|---|

31:0 |

BUF2_ADDR/NXT_DES_ADDR

在DMA采用Ring模式时,这里为BUF2_ADDR,而采用Chain模式时,这里为NXT_DES_ADDR。

BUF2_ADDR

Buffer2 Address,Buffer2地址指针,Buffer2的物理地址。

NXT_DES_ADDR

Next Descriptor Address,下一个描述符的地址,指向下一个描述符的物理地址,从而将描述符连接起来。

|

11.3.2.9.5. 接收描述符RDES4

Bit |

域描述 |

|---|---|

31:21 |

Reserved

|

20:18 |

VLAN_TAG_PRI_V

VLAN Tag Priority Value,此域内容填入接收到的包的VLAN TAG用户值域。

|

17 |

AV_TAG_PKT_RCD

AV Tagged Packet Received,此位置1表示接收到带AV标签的数据包。

|

16 |

AV_PKT_RCD

AV Packet Received,此位置1表示接收到AV包。

|

15 |

Reserved

|

14 |

TMSTMP_DRP

Timestamp Dropped,时钟戳丢失,由于RXFIFO溢出,导致时钟戳丢失。

0x0:无效

0x1:时钟戳丢失

|

13 |

PTP_VER

PTP Version,PTP版本。

0x0:IEEE1588

0x1:IEEE1588V2

|

12 |

RX_PTP_FRM

Received PTP Frame Type,接收到PTP帧的类型。

0x0:接收到PTP报文通过UDP-IPV4或UDP-IPV6的形式传送

0x1:接收到PTP报文直接通过以太网帧形式传送

|

11:8 |

PTP_RX_MSG_TYP

Received PTP Message Type,接收到的PTP消息报文类型。

0x0:无PTP报文

0x1:SYNC报文

0x2:Follow Up报文

0x3:Delay_Req报文

0x4:Delay_Resp报文

0x5:Pdelay_Req报文

0x6:Pdelay_Resp报文

0x7:Pdelay_Resp_Follow_Up报文

0x8:Announce报文

0x9:Management报文

0xA:Signaling报文

0xB~0xE:Reserved

0xF:PTP Packet with Reserved message type

|

7 |

RX_IPV6_PKT

Received IPV6 Packet,接收到IPV6包。

0x0:无效

0x1:接收到的IP包为IPV6包

|

6 |

RX_IPV4_PKT

Received IPV4 Packet,接收到IPV4包。

0x0:无效

0x1:接收到的IP包为IPV4包

|

5 |

DIS_IP_CHSUM

Disable IP Checksum Function,关闭IP校验和功能。

0x0:未关闭

0x1:关闭IP校验和功能

|

4 |

IP_PL_ERR

IP Payload Error,IP包校验错误,接收到的IP包的TCP/UDP/ICMP的校验和错误,或长度错误。

0x0:无错误

0x1:出现IP包校验和错误

|

3 |

IP_HD_ERR

IP Header Error,接收到的IP包的首部校验和与计算的校验和不一致,或者IP版本与Ethernet Type域值

不一致。

0x0:无错误

0x1:出现首部校验和错误

|

2:0 |

IP_PKT_TYP

IP Packet Type,IP包类型,此域只有在BIT6/7生效时才有效。

0x0:未知类型

0x1:UDP包

0x2:TCP包

0x3:ICMP包

others:Reserved

|

11.3.2.9.6. 接收描述符RDES6

Bit |

域描述 |

|---|---|

31:0 |

RX_STMP_LO

Receive Timestamp Low 32bit,接收时间戳的低32位,此域由DMA自动填写,与TDES7的高32bit组成完整

的时间戳。

|

11.3.2.9.7. 接收描述符RDES7

Bit |

域描述 |

|---|---|

31:0 |

RX_STMP_HI

Receive Timestamp High 32bit,发送时间戳的高32位,此域由DMA自动填写,与TDES7的低32bit组成完整

的时间戳。

|

11.3.2.10. IEEE1588

11.3.2.10.1. 时钟戳收发

IEEE1588 时钟戳的收发,在MAC发送或接收到报文后,则触发时钟戳的捕捉,对应的发送或接收描述符会记录相应的Timestamp信息在TDES6、TDES7和RDES6、RDES7。为了让DMA能够记录Timestamp,寄存器ALT_DES_SIZ = 1,配置描述符的大小为8 words。同时TDES0的TTSE(Transmit Timestamp Enable)需要使能。而接收需在Timestamp控制寄存器上配置对应的接收帧类型使能即可。

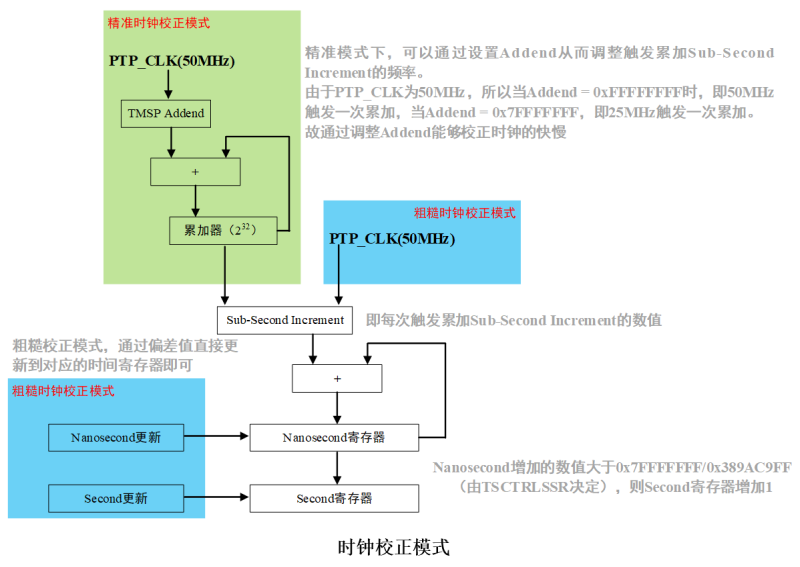

11.3.2.10.2. 时钟校准

IEEE1588功能支持内部系统时钟的校准,可以支持粗糙和精准校准两种方式。粗糙的校准通过PTP协议报文的交互计算出时钟偏差,通过Update寄存器更新系统时间;精准的校准则通过PTP协议报文的交互计数时钟偏差的频率比,更新Timestamp Addend寄存器,实现同步时钟。

图 11.8 PTP时钟校准