9.8.2. 功能描述

9.8.2.1. Audio Codec时钟

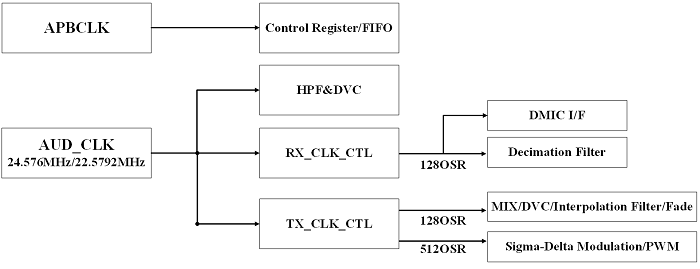

图 9.63 Audio Codec时钟框图

Audio Codec的时钟框图如上图所示,APBCLK用于控制寄存器以及FIFO,AUD_CLK(24.576MHz/22.5792MHz由CMU分频所得)则同时控制TX(播放)和RX(录音)部分。

RX部分通过寄存器FS_DMIC_IN配置了RX的采样频率,那么相应的过采样率128倍的时钟则提供给DMIC I/F模块以及Decimation Filter,RX部分的HPF以及DVC的时钟则由AUD_CLK直接提供。

TX部分通过寄存器FS_OUT配置了TX的采样频率,那么相应的过采样率128倍的时钟则提供MIX、DVC、Interpolation Filter、Fade模块,过采样率512倍的时钟则提供Sigma-Delta Modulation、PWM模块。

9.8.2.2. Audio Codec信号通路

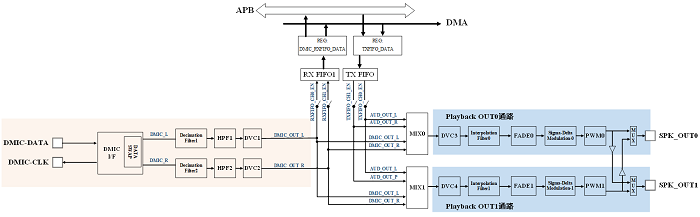

图 9.64 Audio Codec信号通路

上图为Audio Codec的信号通路示意图。

通过RXFIFO_CH0_EN/ RXFIFO_CH1_EN,可以分别控制DMIC通道的左/右声道的数据填入RXFIFO1。

DMIC左声道的数据(即DMIC_CLK为低时的DMIC_DATA数据)填入RXFIFO1的Channel0,DMIC右声道的数据(即DMIC_CLK为高时的DMIC_DATA数据)填入RXFIFO1的Channel1。若需要交叉DMIC的左右通道的数据,可以通过DMIC I/F模块的DATA SWAP功能,可以将DMIC的左/右声道的数据交换。

通过TXFIFO_CH0_EN/ TXFIFO_CH1_EN,分别控制TXFIFO中的左/右声道的数据,如若需要交叉OUT0通路和OUT1通路的数据,可以通过MIX0、MIX1的寄存器配置,实现OUT0/1通路的数据交换。

9.8.2.3. 抽值滤波器

Audio codec内置2路抽值滤波器,用于2x DMIC通路。

DMIC对应的抽值滤波器Decimation Filter1/2的下采样可通过寄存器选择为64/128倍。

9.8.2.4. 高通滤波器

高通滤波器(HPF,-3dB cutoff < 1Hz),可以通过寄存器HPF_EN使能,此滤波器主要用于滤除ADC Offset。其中,寄存器HPF_Coefficient用于配置HPF的系数,寄存器HPF_Gain用于配置HPF的增益。如若高通滤波器未使能工作,则直接旁通输入信号到下一个模块。

9.8.2.5. 数字音量控制(DVC)

在每个TX、RX通路上均有设计独立的DVC模块,可以通过DVC_EN使能,如若未使能,则旁通输入信号到下一个模块。DVC的可调范围为-119.25dB to 71.25dB,步进0.75dB。

9.8.2.6. 插值滤波器

插值滤波器(Interpolation Filter)实现128倍的上采样,实现抽值滤波器的相反功能,依次采用半带滤波、CIC补偿滤波和CIC插值滤波,实现的上采样倍数分别为2、2、32。经过插值滤波器,得到高采样率的数字信号。

9.8.2.7. Sigma-Delta Modulation

经过插值滤波后,进行数字Sigma-Delta算法,获得PDM信号。其中,Sigma-Delta调制采用2阶-1bit结构。

9.8.2.8. PWM

PWM模块用于对PDM进行调制,调制方式为0代表25%占空比的时钟信号,1代表75%占空比的时钟信号,时钟频率为PDM的采样时钟频率,即128 * FS_OUT。另外,PWM支持差分模式,若PWM0使能差分模式,那么SPK_OUT0则输出PWM0,SPK_OUT1则输出反相PWM0。此时PWM1应配置为关闭状态。

9.8.2.9. 中断

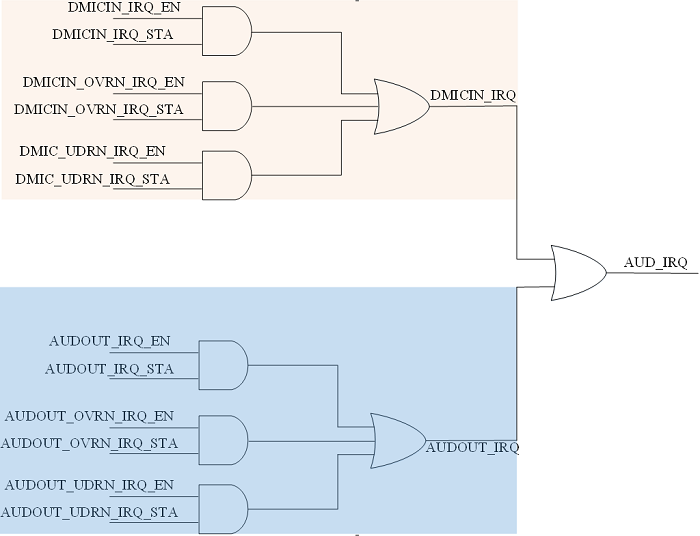

图 9.65 中断信号

由上图所示可看出Audio Codec的中断信号,各信号的具体如下:

DMICIN_IRQ_STA为DMIC的RXFIFO接收到有效数据(即RXFIFO的数据多于阈值DMIC_RXTH)时产生的中断信号,此时也会相应的产生DMICIN_DRQ信号;

DMICIN_OVRN_IRQ_STA为DMIC的RXFIFO出现上溢出中断;

DMICIN_UDRN_IRQ_STA为DMIC的RXFIFO出现下溢出中断;

AUDOUT_IRQ_STA为TXFIFO数据空间充足(即TXFIFO的剩余的数据空间多于TXFIFO_TH)时产生的中断信号,此时也会相应的产生AUDOUT _DRQ信号;

AUDOUT_OVRN_IRQ_STA为DMIC的RXFIFO出现上溢出中断;

AUDOUT _UDRN_IRQ_STA为DMIC的RXFIFO出现下溢出中断。

9.8.3. 编程指南

9.8.3.1. 常用场景参数配置

使用DMIC通路收音,双通道收音,主时钟为24.576MHz,采样频率为48kHz,过采样率为128:

RX DMIC接口控制寄存器

RX_DMIC_IF_CTL[11:9] = 0x0 //延时接收功能,根据需求配置

RX_DMIC_IF_CTL[8] = 0x0 //配置抽取滤波器1、2的下采样率为128

RX_DMIC_IF_CTL[7:6] = 0x3 //使能两路抽值滤波器

RX_DMIC_IF_CTL[5] = 0x0 //DMIC左右通道数据不互换

RX_DMIC_IF_CTL[4] = 0x1 //DMIC接口使能,输出DMIC_CLK

RX_DMIC_IF_CTL[3:1] = 0x0 //DMIC采样频率配置48kHz

RX_DMIC_IF_CTL[0] = 0x0 //主时钟配置24.576MHz

RX HPF1&2控制寄存器

RX_HPF1&2_CTL[1:0] = 0x3 //使能高通滤波器

RX DVC1&2控制寄存器

RX_DVC1&2_CTL[31:24] = 0xA0 //DVC2数字音量控制模块,根据需求配置

RX_DVC1&2_CTL[23:16] = 0xA0 //DVC1数字音量控制模块,根据需求配置

RX_DVC1&2_CTL[1:0] = 0x3 //使能两路DVC

DMIC RXFIFO控制寄存器

DMIC_RXFIFO_CTL[1:0] = 0x3 //使能双通道RXFIFO

使用双通道播放,主时钟为24.576MHz,采样频率为48kHz ,过采样率为128

TX MIXER控制寄存器

TX_MIXER_CTL[31:30] = 0x0 //不使能混音功能,通路配置为AUD_OUT

TX_MIXER_CTL[12:8] = 0x2 //通路配置为AUD_OUT_R

TX_MIXER_CTL[4:0] = 0x1 //通路配置为AUD_OUT_L

TX DVC3&4控制寄存器

TX_DVC3&4_CTL[31:24] = 0xA0 //DVC4数字音量控制模块,根据需求配置

TX_DVC3&4_CTL[23:16] = 0xA0 //DVC3数字音量控制模块,根据需求配置

TX_DVC3&4_CTL[1:0] = 0x3 //使能两路DVC

TX Playback控制寄存器

TX_PLAYBACK_CTL[14:12] = 0x0 //延时输出功能,根据需求配置

TX_PLAYBACK_CTL[10:8] = 0x3 //滤波输出Shift比特数配置为默认值13比特(推荐使用默认值)

TX_PLAYBACK_CTL[6:4] = 0x7 //插值滤波器使能

TX_PLAYBACK_CTL[3:0] = 0x0 //主时钟配置24.576MHz,采样频率配置48kHz

TX SDM控制寄存器

TX_SDM_CTL[31:8] = 0x11011 //SDM增益默认值配置(推荐使用默认值)

TX_SDM_CTL[1:0] = 0x3 //SDM使能

TX PWM控制寄存器

TX_PWM_CTL[6:0] = 0x11 //PWM使能并配置为输出PWM调制信号

TX FIFO控制寄存器

TXFIFO_CTL[2:0] = 0x3 //使能TXFIFO通道,下溢出时发送0