7.2.2. 功能描述

7.2.2.1. LDO1x 默认状态

LDO1x 可调范围为 0.90V~1.90V,不同封装芯片表现有两个用途:

SoC CORE供电,默认为打开

SoC 外设供电,默认为关闭

为了区分 LDO1x 默认状态,通过模拟PAD LDO1x_EN悬空或者打线到地做区分,由模拟电路在3.3V电源域实现。

用途 |

PAD_LDO1x_EN |

|---|---|

CORE供电(默认打开) |

悬空(内部已上拉) |

外设供电(默认关闭) |

打线到地 |

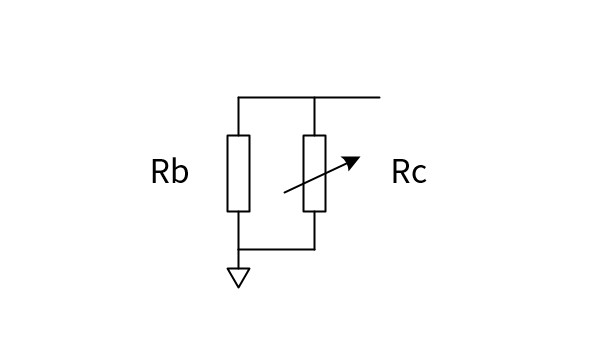

7.2.2.2. CALI RES

校准电阻结构如 图 7.4 ,由 Rb和Rc两部分并联实现

Rb 基准电阻:提供固定阻值

Rc 校准电阻:提供可配置的电阻值,通过改变CAL_VAL改变电阻值,Rc计算公式如下表所示。

图 7.4 校准电阻

- |

- |

CAL_VAL |

Rb阻值Ω |

Rc阻值Ω |

Rb//Rc阻值Ω |

||

|---|---|---|---|---|---|---|---|

模块 |

需求阻值Ω |

默认值 |

理论 |

计算公式 |

理论默认值 |

计算公式 |

理论默认值 |

USB |

200 |

96 |

320.36 |

51257.7/CAL_VAL |

534 |

Rb*Rc/(Rb+Rc) |

200 |

7.2.2.3. PSEN

PSEN (Process Sensor,工艺传感器),用于监测制造工艺下数字电路的频率范围,典型应用如下:

CP测试阶段,根据PSEN进行分BIN操作,典型如分CPU 1GHz和800MHz两种DIE;

方案应用阶段,根据PSEN来进行调频调压,达到降低功耗的目的

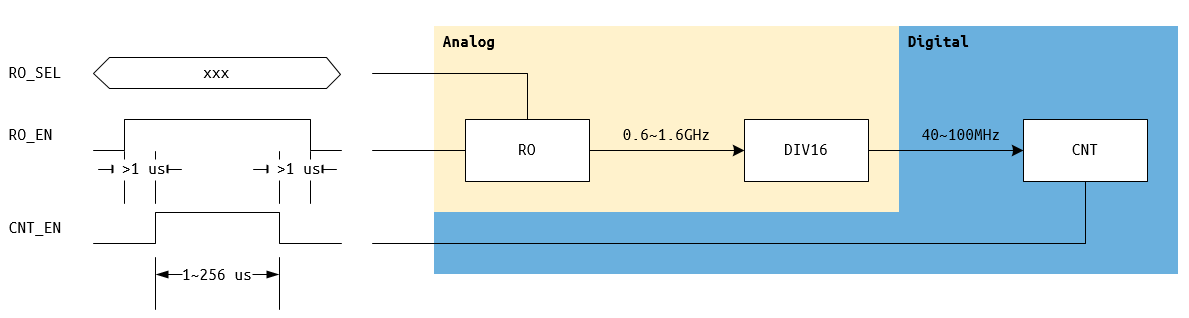

PSEN工作流程如下,参考 图 7.5:

软件配置好测试参数(RO_SEL, CNT_TIME),打开测试(PSEN_EN=1)

PSEN_EN=1触发数字电路打开RO_EN,模拟电路RO开始振荡工作起来,并进行16分频得到低频时钟,用于数字电路计数

数字电路打开RO_EN后延迟打开CNT_EN,CNT开始计数,CNT_TIME时间后,自动关闭CNT_EN,并延时关闭RO_EN,将PSEN_EN清零表示测试完成

软件检测到PSEN_EN清零后,读取CNT_VAL值为当前PSEN的速度;

软件重复①~④测试更多的RO#.

图 7.5 PSEN工作流程

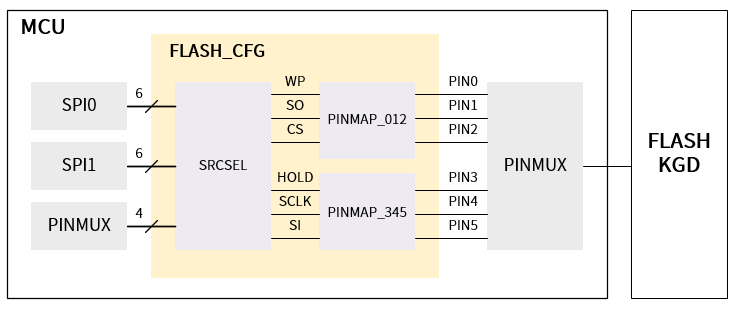

7.2.2.4. FLASH_CFG

芯片内部合封了FLASH,对合封的FLASH进行烧写和读写访问,通过FLASH_CFG子模块实现。

FLASH_CFG如 图 7.6 ,包含了SRCSEL和PINMAP两个模块。

SRCSEL用于选择控制来源,有以下三种控制源:

SPI0

SPI1

PINMUX:主要用于进行FLASH裸片烧录

PINMAP用于对引脚进行映射,兼容各种FLASH DIE的出PIN,分为两组,每组3个引脚:

PINMAP_012: WP MISO CS -> PIN0 PIN1 PIN2

PINMAP_345: HOLD SCLK MOSI -> PIN3 PIN4 PIN5

图 7.6 FLASH_CFG 框图