7.1.2. 功能描述

7.1.2.1. PLL

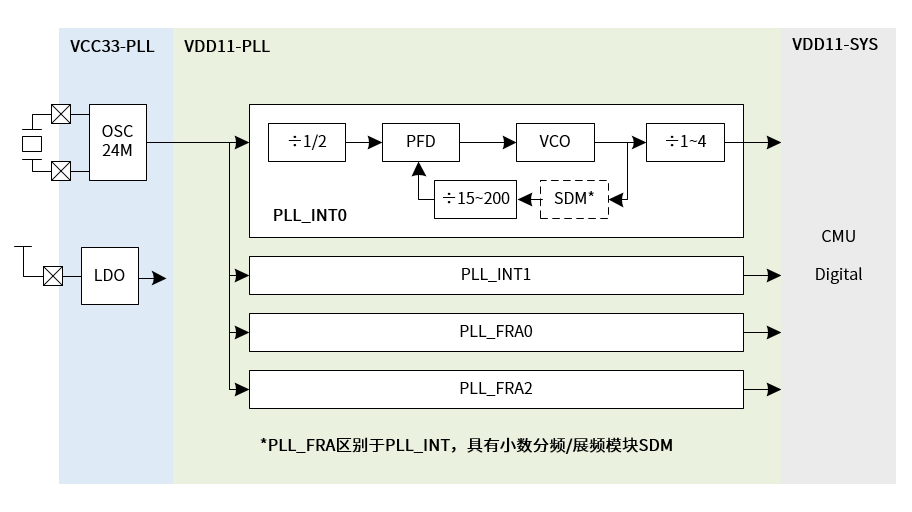

模拟电路PLL用于产生时钟供给整个芯片,总共4个PLL, 用途及特性如 表 7.1 所示。

名称 |

用途 |

典型频率 |

展频 |

|---|---|---|---|

PLL_INT0 |

CPU/DM

|

504MHz

|

不支持 |

PLL_INT1 |

AXI/AHB/APB/

CE/DE/GE/VE/DVP/

UART/PWM

I2S/AUDIO

|

1.2GHz

|

不支持 |

PLL_FRA0 |

XSPI/SPI/SDMC

|

800MHz

|

展频 |

PLL_FRA2 |

LCD/LVDS/MIPI_DSI

|

展频 |

PLL内部结构如 图 7.1 所示, PLL频率计算公式为:PLL_OUT = 24MHz÷(P+1)×(N+1+(F÷(2^17-1)))÷(M+1)。

图 7.1 CMU PLL 内部结构

7.1.2.2. CLKOUT

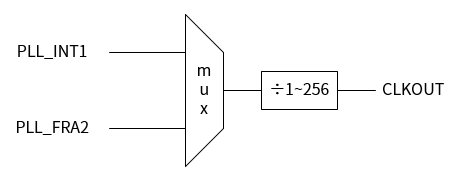

时钟输出用于输出时钟给芯片外设使用, 总共4路CLKOUT, 可选来源为PLL_INT1/PLL_FRA2,可配置1~256除频, CLKOUT通路如 图 7.2 所示。

图 7.2 CMU CLKOUT 通路

7.1.2.3. OSC24M和XTAL

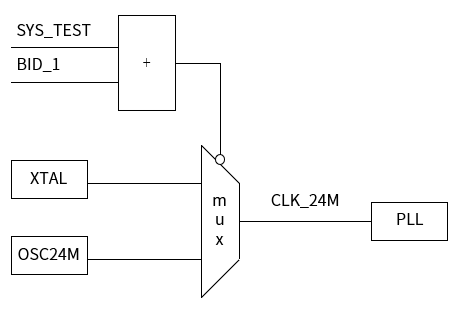

时钟源输入用于给芯片提供时钟,总共两个时钟源选择,可选内部OSC24M或者外部XTAL, 当引脚SYS_TEST配置的值为1时,无论BID_1为何值,只能选择外部XTAL作为芯片时钟源输入。 当引脚SYS_TEST配置的值为0时,根据BID_1的值,选择芯片的输入时钟源,若BID_1的值为1, 则选择外部XTAL时钟源,若BID_1的值为0,则选择内部OSC24M时钟源, 时钟源选择如 图 7.3 所示。

图 7.3 CMU 时钟源选择

7.1.2.4. 模块时钟

模块名称 |

总线时钟 |

模块时钟源 |

模块时钟极限频率 |

备注 |

|---|---|---|---|---|

E907 CORE |

- |

PLL_INT0 |

504MHz |

- |

E907 PLIC |

- |

PLL_INT0÷2 |

252MHz |

- |

E907 CLINT |

- |

PLL_INT0÷2 |

252MHz |

- |

E907 DM |

- |

CLK_24M |

24MHz |

- |

AXI |

AXI |

- |

240MHz |

- |

AHB |

AHB |

- |

240MHz |

- |

APB0 |

APB0 |

- |

100MHz |

- |

APB1 |

APB1 |

- |

24MHz |

- |

BROM |

AXI |

- |

- |

- |

SRAM |

AXI |

- |

- |

- |

AHB Matrix |

AHB |

- |

- |

- |

DMA |

AHB |

- |

- |

- |

CE |

AHB |

PLL_INT1 |

200MHz |

- |

USB DEV |

AHB |

- |

- |

- |

USB HOST |

AHB |

- |

- |

- |

USB PHY |

- |

CLK_24M |

- |

- |

EMAC |

AHB |

PLL_INT1 |

50MHz |

- |

XSPI |

AHB |

PLL_FRA0 |

400MHz |

- |

SPI0 |

AHB |

PLL_FRA0 |

100MHz |

- |

SPI1 |

AHB |

PLL_FRA0 |

100MHz |

- |

SPI2 |

AHB |

PLL_FRA0 |

100MHz |

- |

SPI3 |

AHB |

PLL_FRA0 |

100MHz |

- |

SDMC0 |

AHB |

PLL_FRA0 |

200MHz |

- |

SDMC1 |

AHB |

PLL_FRA0 |

200MHz |

- |

PBUS |

AHB |

- |

- |

- |

SYSCFG |

APB0 |

CLK_24M |

24MHz |

- |

CMU |

APB0 |

- |

- |

- |

SPI_ENC |

APB0 |

HCLK |

- |

- |

AXICFG |

APB0 |

- |

- |

- |

MTOP |

APB0 |

- |

- |

- |

I2S |

APB0 |

PLL_INT1 |

26MHz |

- |

AUDIO |

APB0 |

PLL_INT1 |

26MHz |

- |

GPIO |

APB0 |

- |

- |

- |

UART0 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART1 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART2 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART3 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART4 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART5 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART6 |

APB0 |

PLL_INT1 |

60MHz |

- |

UART7 |

APB0 |

PLL_INT1 |

60MHz |

- |

LCD |

APB0 |

PLL_FRA2 |

400MHz |

DISP_PIXCLK:200MHz |

LVDS |

APB0 |

PLL_FRA2 |

1000MHz |

DISP_PIXCLK:200MHz |

DSI |

APB0 |

PLL_FRA2 |

1200MHz |

DISP_PIXCLK:200MHz |

DVP |

APB0 |

PLL_INT1 |

200MHz |

- |

DE |

APB0 |

PLL_INT1 |

200MHz |

DISP_PIXCLK:200MHz |

GE |

APB0 |

PLL_INT1 |

200MHz |

- |

VE |

TBD |

PLL_INT1 |

200MHz |

- |

WDOG |

APB1 |

CLK_32K |

32KHz |

- |

WRI |

APB1 |

CLK_24M |

24MHz |

- |

SID |

APB1 |

CLK_24M |

24MHz |

- |

RTC |

APB1 |

OSC_32K |

- |

- |

GTC |

APB1 |

- |

- |

- |

I2C0 |

APB1 |

- |

- |

- |

I2C1 |

APB1 |

- |

- |

- |

I2C2 |

APB1 |

- |

- |

- |

I2C3 |

APB1 |

- |

- |

- |

CAN0 |

APB1 |

- |

- |

- |

CAN1 |

APB1 |

- |

- |

- |

PWM |

APB1 |

PLL_INT1 |

100MHz |

- |

ADCIM |

APB1 |

PLL_INT1 |

100MHz |

- |

GPAI |

APB1 |

- |

- |

- |

RTP |

APB1 |

- |

- |

- |

THS |

APB1 |

- |

- |

- |

CIR |

APB1 |

- |

- |

- |

7.1.2.5. 模块开关时序

USB

打开时序:

ctrl clk 1 -> phy clk 1 -> 100us -> phy rst 1 -> ctrl rst 1

关闭时序:

ctrl rst 0 -> phy rst 0 -> phy clk 0 -> ctrl clk 0

其他模块

打开时序:

mod clk 1 -> bus clk 1 -> rst 1

关闭时序:

rst 0 -> bus clk 0 -> mod clk 0